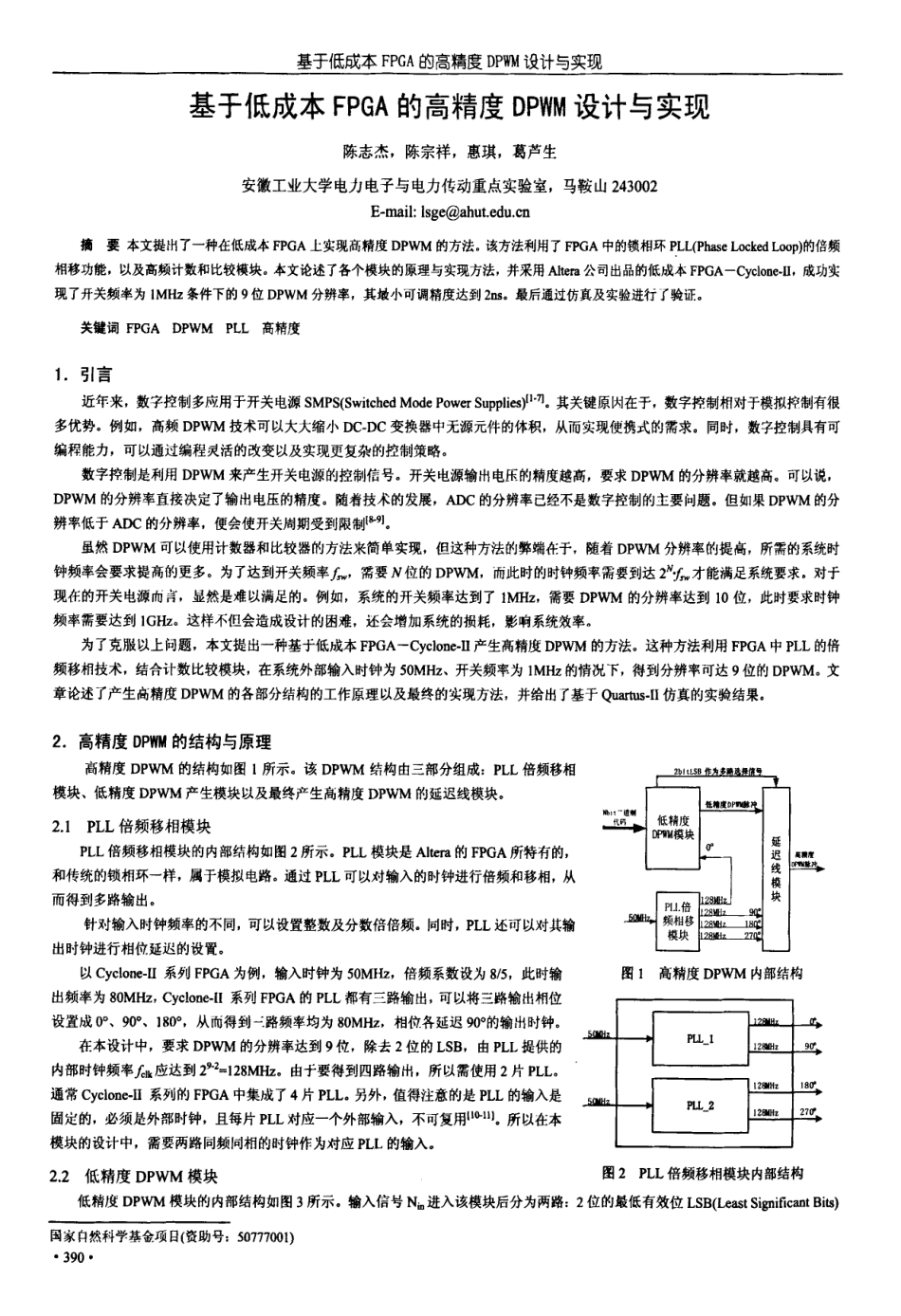

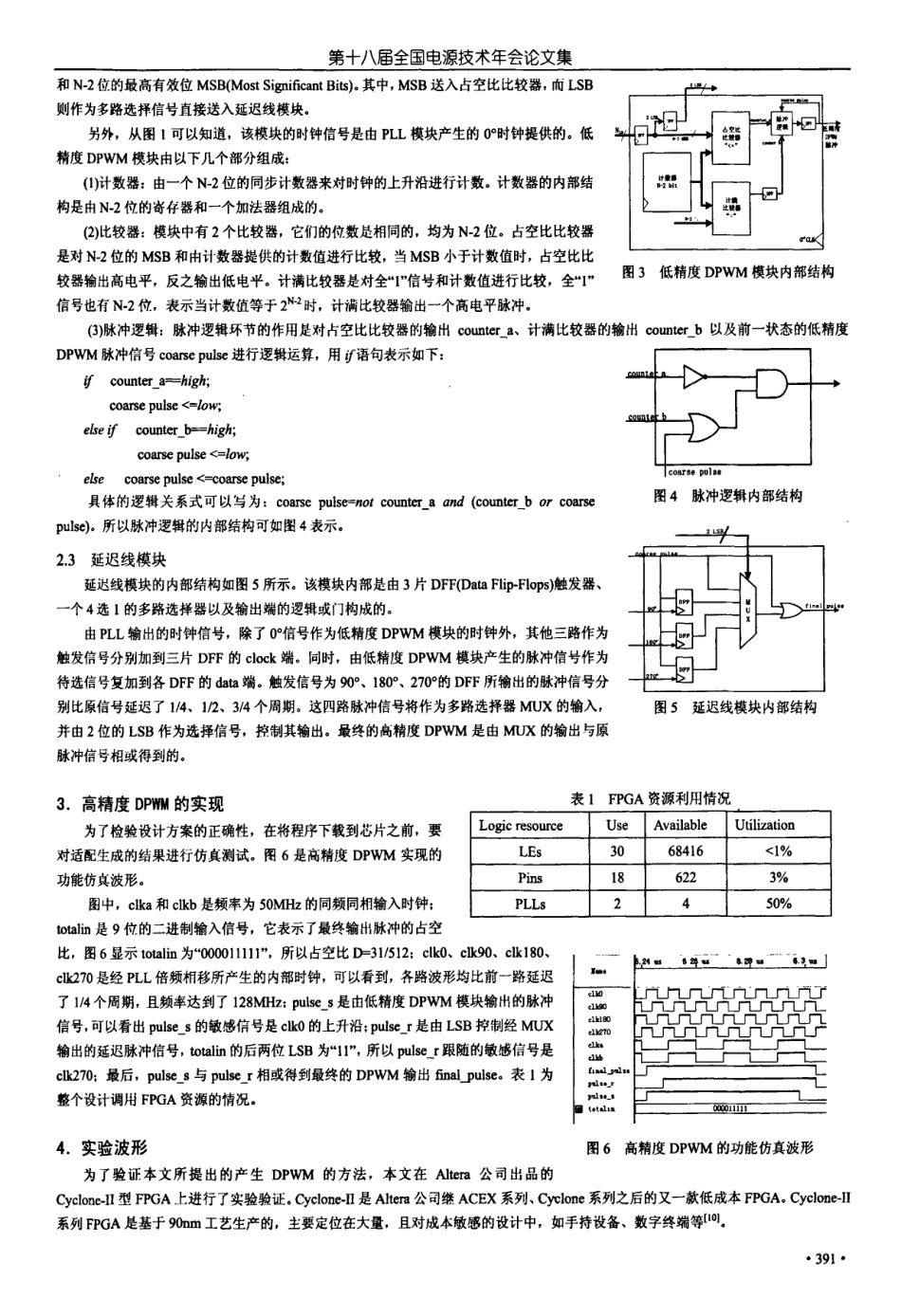

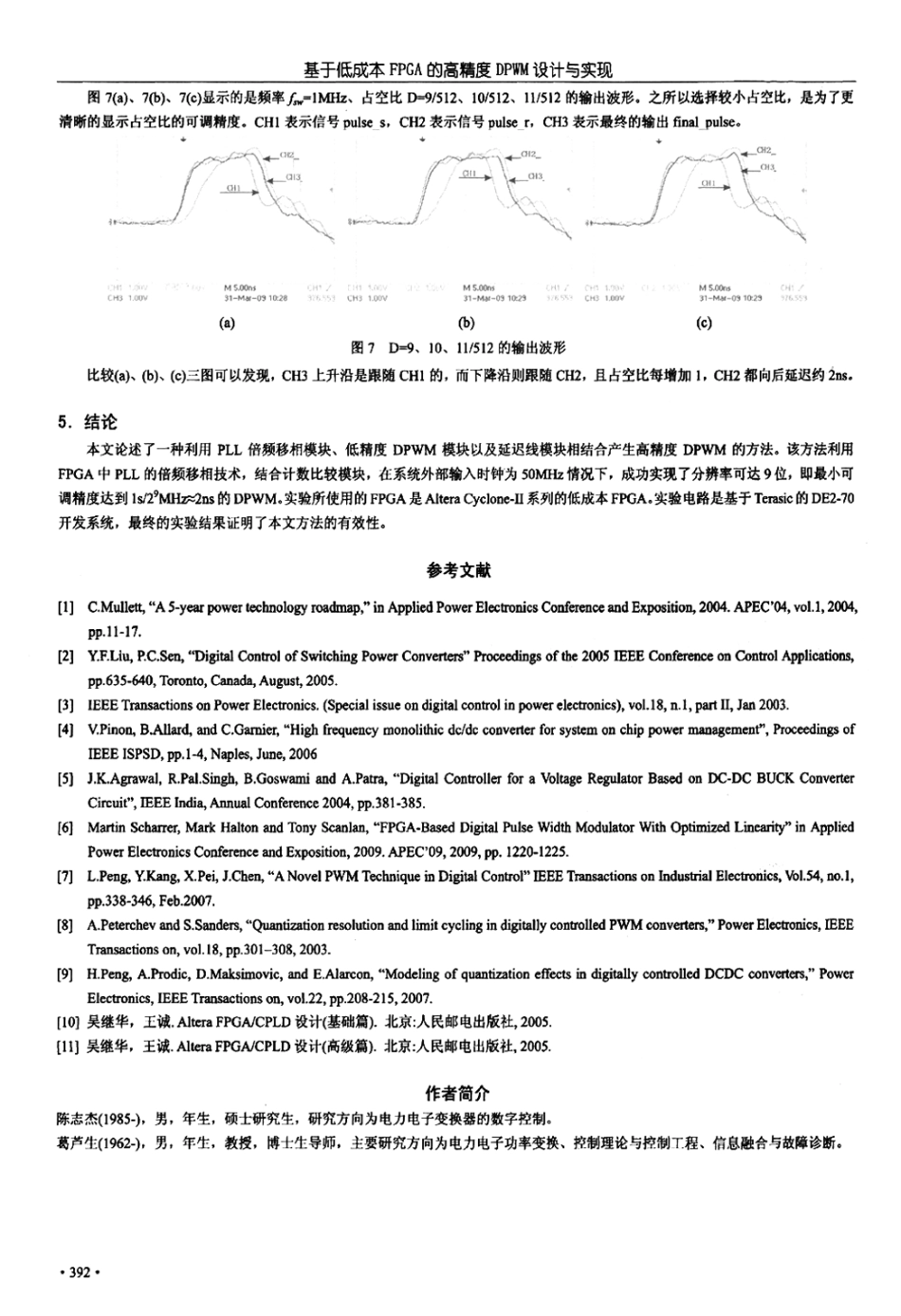

基于低成本FPGA的高精度DPWM设计与实现基于低成本FPGA的高精度DPWM设计与实现陈志杰,陈宗祥,惠琪,葛芦生安徽工业大学电力电子与电力传动重点实验室,马鞍山243002E·mail:lsge@abut.edu.cn摘要本文提出了一种在低成本FPGA上实现高精度DPWM的方法。该方法利用了FPGA中的锁相环PLL(PhaseLockedLoop)的倍频相移功能,以及高频计数和比较模块。本文论述了各个模块的原理与实现方法,并采用Altera公司出品的低成本FPGA--Cyclone.II,成功实现了开关频率为IMHz条件下的9位DPWM分辨率,其最小可调精度达到2ns。最后通过仿真及实验进行了验证。关键词FPGADPWMPLL高精度1.引言近年来,数字控制多应用于开关电源SMPS(SwitchedModePowerSupplies)[1-71。其关键原因在于,数字控制相对于模拟控制有很多优势。例如,高频DPWM技术可以大大缩小DC.DC变换器中无源元件的体积,从而实现便携式的需求。同时,数字控制具有可编稃能力,可以通过编程灵活的改变以及实现更复杂的控制策略。数字控制是利用DPWM来产生开关电源的控制信号。开关电源输}H电压的精度越高,要求DPWM的分辨率就越高。可以说,DPWM的分辨率直接决定了输出电压的精度。随着技术的发展,ADC的分辨率已经不是数字控制的主要问题。但如果DPWM的分辨率低于ADC的分辨率,便会使开关周期受到限制I鲫1。虽然DPWM可以使用计数器和比较器的方法来简单实现,但这种方法的弊端在于,随着DPWM分辨率的提高,所需的系统时钟频率会要求提高的更多。为了达到开关频率名,需要Ⅳ位的DPWM,而此时的时钟频率需要到达2~‰才能满足系统要求。对于现在的开关电源而占,显然是难以满足的。例如,系统的开关频率达到了IMHz,需要DPWM的分辨率达到10位,此时要求时钟频率需要达到IGHz。这样不但会造成设计的困难,还会增加系统的损耗,影响系统效率。为了克服以上问题,本文提出一种基于低成本FPGA--Cyclone.Ⅱ产生高精度DPWM的方法。这种方法利用FPGA中PLL的倍频移相技术,结合计数比较模块,在系统外部输入时钟为50MHz、开关频率为1MHz的情况下,得到分辨牢可达9位的DPWM。文章论述了产生高精度DPWM的各部分结构的工作原理以及最终的实现方法,并给出了基于Quartus.II仿真的实验结果。2.高精度DPWM的结构与原理高精度DPVn'v[的结构如图l所示。该DPWM结构由三部分组成:PLL倍频移相模块、低精度DPWM产生模块以及最终产生高精度DPWM的延迟线模块。2.1PLL倍频移相模块PLL倍频移相模块的内部结构如图2所示。PL...