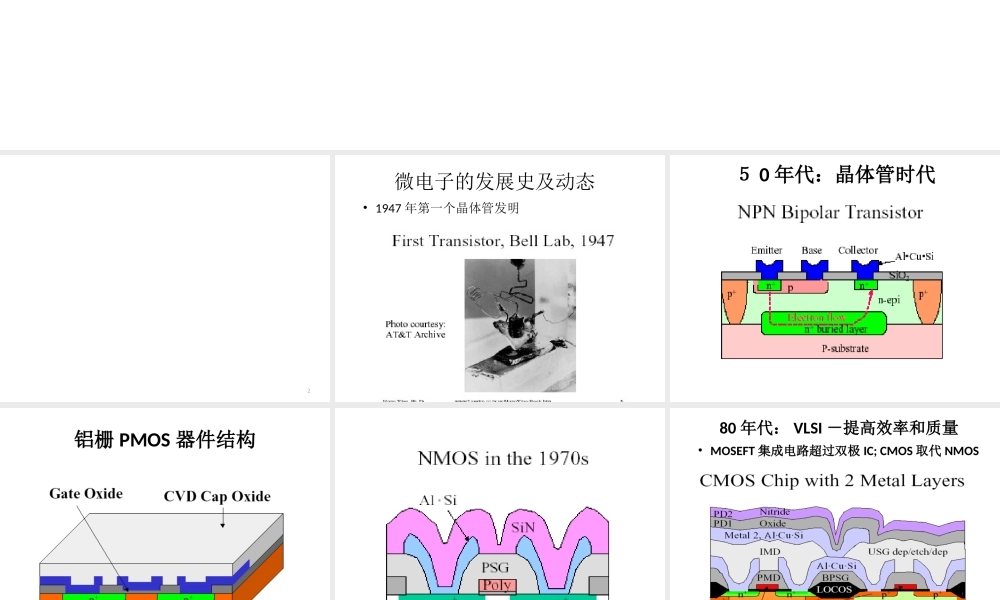

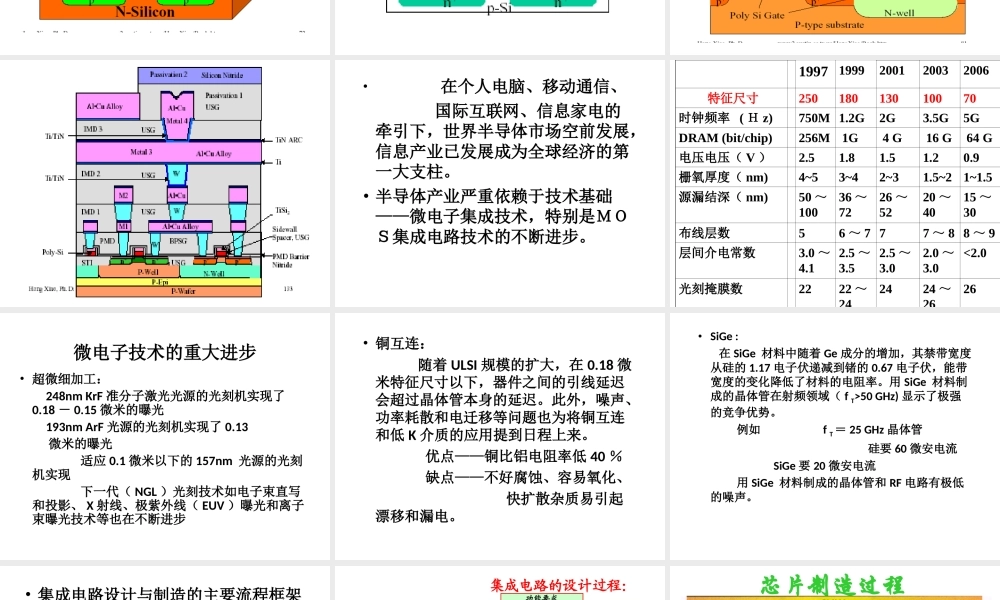

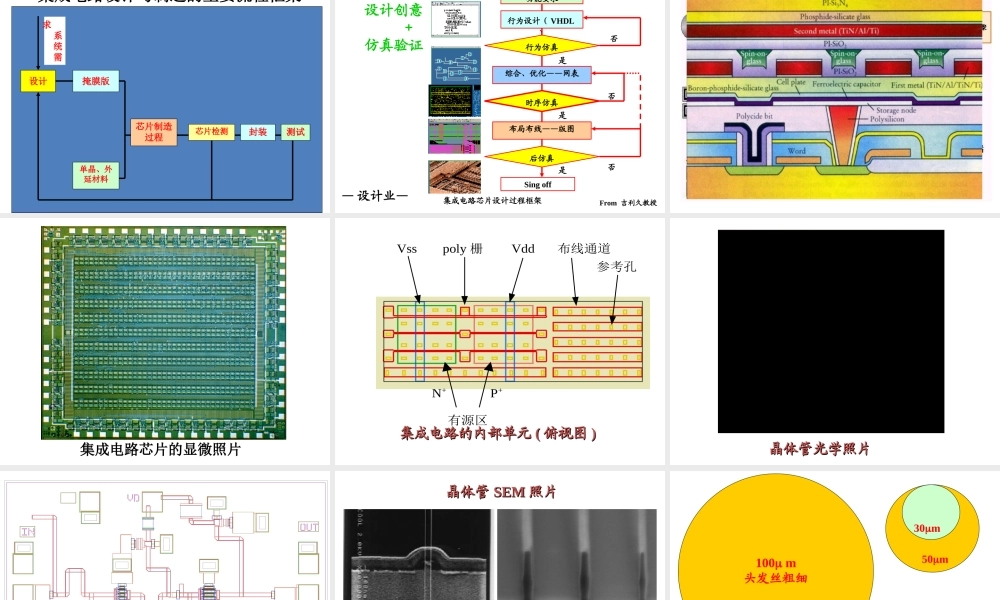

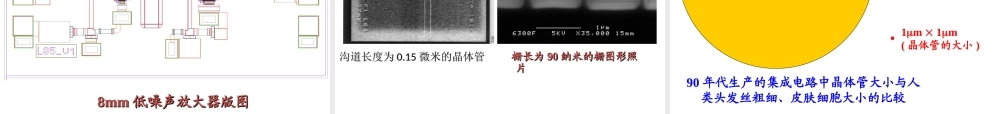

集成电路制造工艺集成电路制造工艺2微电子的发展史及动态•1947年第一个晶体管发明50年代:晶体管时代铝栅PMOS器件结构80年代:VLSI-提高效率和质量•MOSEFT集成电路超过双极IC;CMOS取代NMOS•在个人电脑、移动通信、国际互联网、信息家电的牵引下,世界半导体市场空前发展,信息产业已发展成为全球经济的第一大支柱。•半导体产业严重依赖于技术基础——微电子集成技术,特别是MOS集成电路技术的不断进步。19971999200120032006特征尺寸25018013010070时钟频率(Hz)750M1.2G2G3.5G5GDRAM(bit/chip)256M1G4G16G64G电压电压(V)2.51.81.51.20.9栅氧厚度(nm)4~53~42~31.5~21~1.5源漏结深(nm)50~10036~7226~5220~4015~30布线层数56~777~88~9层间介电常数3.0~4.12.5~3.52.5~3.02.0~3.0<2.0光刻掩膜数2222~242424~2626微电子技术的重大进步•超微细加工:248nmKrF准分子激光光源的光刻机实现了0.18-0.15微米的曝光193nmArF光源的光刻机实现了0.13微米的曝光适应0.1微米以下的157nm光源的光刻机实现下一代(NGL)光刻技术如电子束直写和投影、X射线、极紫外线(EUV)曝光和离子束曝光技术等也在不断进步•铜互连:随着ULSI规模的扩大,在0.18微米特征尺寸以下,器件之间的引线延迟会超过晶体管本身的延迟。此外,噪声、功率耗散和电迁移等问题也为将铜互连和低K介质的应用提到日程上来。优点——铜比铝电阻率低40%缺点——不好腐蚀、容易氧化、快扩散杂质易引起漂移和漏电。•SiGe:在SiGe材料中随着Ge成分的增加,其禁带宽度从硅的1.17电子伏递减到锗的0.67电子伏,能带宽度的变化降低了材料的电阻率。用SiGe材料制成的晶体管在射频领域(fT>50GHz)显示了极强的竞争优势。例如fT=25GHz晶体管硅要60微安电流SiGe要20微安电流用SiGe材料制成的晶体管和RF电路有极低的噪声。•集成电路设计与制造的主要流程框架设计芯片检测单晶、外延材料掩膜版芯片制造过程封装测试系统需求集成电路的设计过程:设计创意+仿真验证集成电路芯片设计过程框架From吉利久教授是功能要求行为设计(VHDL)行为仿真综合、优化——网表时序仿真布局布线——版图后仿真否是否否是Singoff—设计业——制造业—芯片制造过程由氧化、淀积、离子注入或蒸发形成新的薄膜或膜层曝光刻蚀硅片测试和封装用掩膜版重复20-30次集成电路芯片的显微照片Vsspoly栅Vdd布线通道参考孔有源区N+P+集成电路的内部单元集成电路的内部单元((俯视图俯视图))晶体管光学照片晶体管...