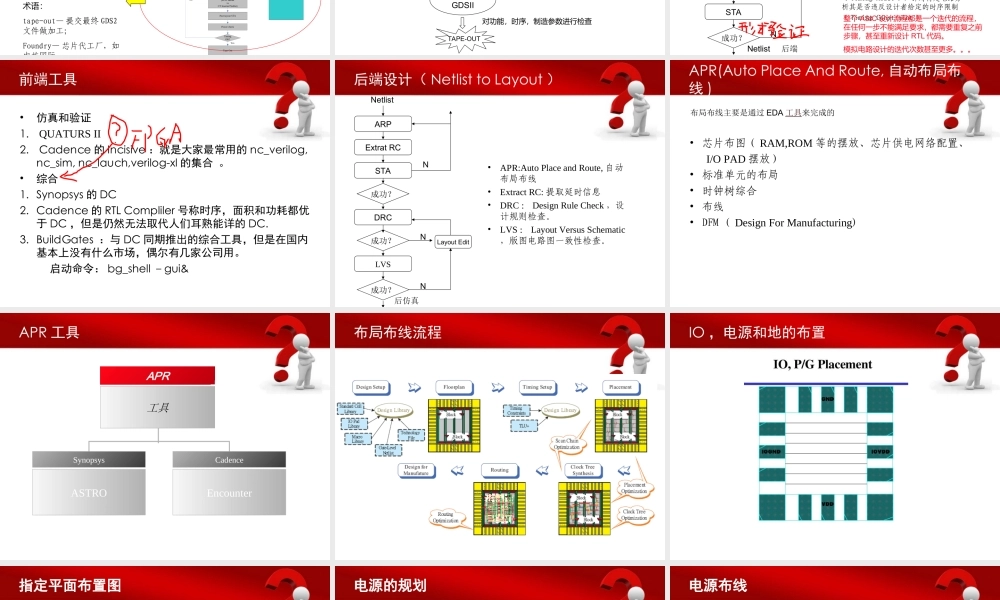

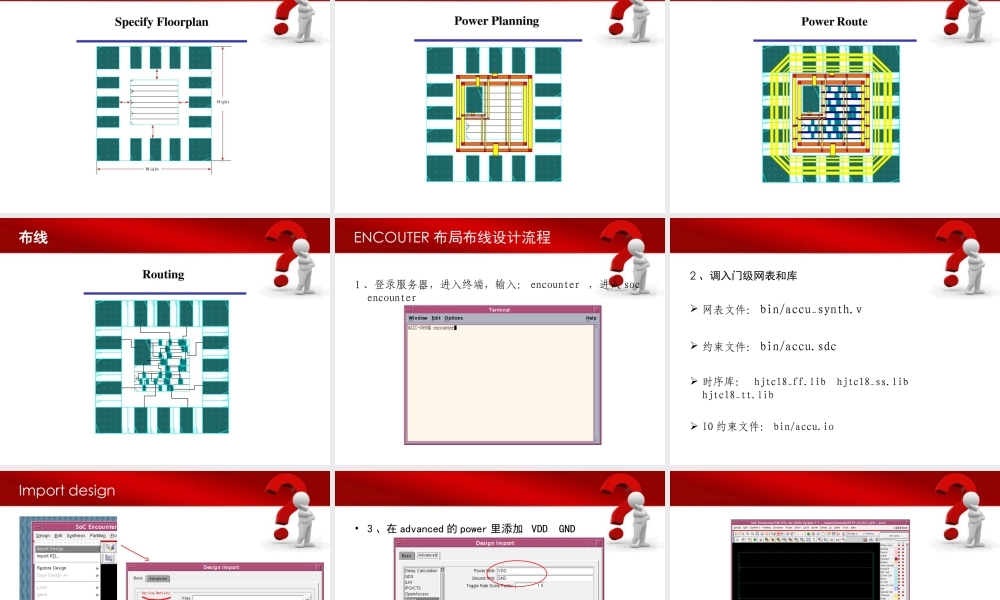

模拟?数字?OR数字IC设计流程数字IC设计流程制定芯片的具体指标用系统建模语言对各个模块描述RTL设计、RTL仿真、硬件原型验证、电路综合版图设计、物理验证、后仿真等具体指标•制作工艺•裸片面积•封装•速度•功耗•功能描述•接口定义前端设计与后端设计Architechturalspecs&RTLcodingConcept+MarketResearchRTLsimulationLogicSynthesis,Optimization&ScanInsertionFormalVerification(RTLvsGates)Pre-layoutSTATimingOK?Floorplanning&Placement,CTInsertionAutoRoutingFormalVerification(ScanInsertedNetlistvsCTInsertedNetlist)DRC,LVS,ECOPost-layoutSTATimingOK?FormalVerification(ECONetlistvsCTInsertedNetlist)PowercheckNoYesNoTapeOutYesDCMODELSIMMBISTARCHITECTFORMALITYPTAstroAstroRailFORMALITYPTHerculesCaliberVirtuoso数字前端设计(front-end)以生成可以布局布线的网表(Netlist)为终点。数字后端设计(back-end)以生成可以可以送交foundry进行流片的GDS2文件为终点。术语:tape-out—提交最终GDS2文件做加工;Foundry—芯片代工厂,如中芯国际算法模型c/matlabcodeRTLHDLvhdl/verilogNETLISTverilogStandcelllibraryLAYOUTGDSII对功能,时序,制造参数进行检查TAPE-OUT综合工具根据基本单元库的功能-时序模型,将行为级代码翻译成具体的电路实现结构布局布线工具根据基本单元库的时序-几何模型,将电路单元布局布线成为实际电路版图数字IC设计流程前端设计(RTLtoNetlist)•RTL(RegisterTransferLevel)设计利用硬件描述语言,如verilog,对电路以寄存器之间的传输为基础进行描述•综合:将RTL级设计中所得的程序代码翻译成实际电路的各种元器件以及他们之间的连接关系,可以用一张表来表示,称为门级网表(Netlist)。•STA(StaticTimingAnalysis,静态时序分析):套用特定的时序模型(TimingModel),针对特定电路分析其是否违反设计者给定的时序限制(TimingConstraint)RTLCode风格代码检查功能仿真逻辑综合成功?综合后仿真成功?STA成功?代码修改约束修改NNNNetlist后端整个ASIC设计流程都是一个迭代的流程,在任何一步不能满足要求,都需要重复之前步骤,甚至重新设计RTL代码。模拟电路设计的迭代次数甚至更多。。。前端工具•仿真和验证1.QUATURSII2.Cadence的Incisive:就是大家最常用的nc_verilog,nc_sim,nc_lauch,verilog-xl的集合。•综合1.Synopsys的DC2.Cadence的RTLCompliler号称时序,面积和功耗都...