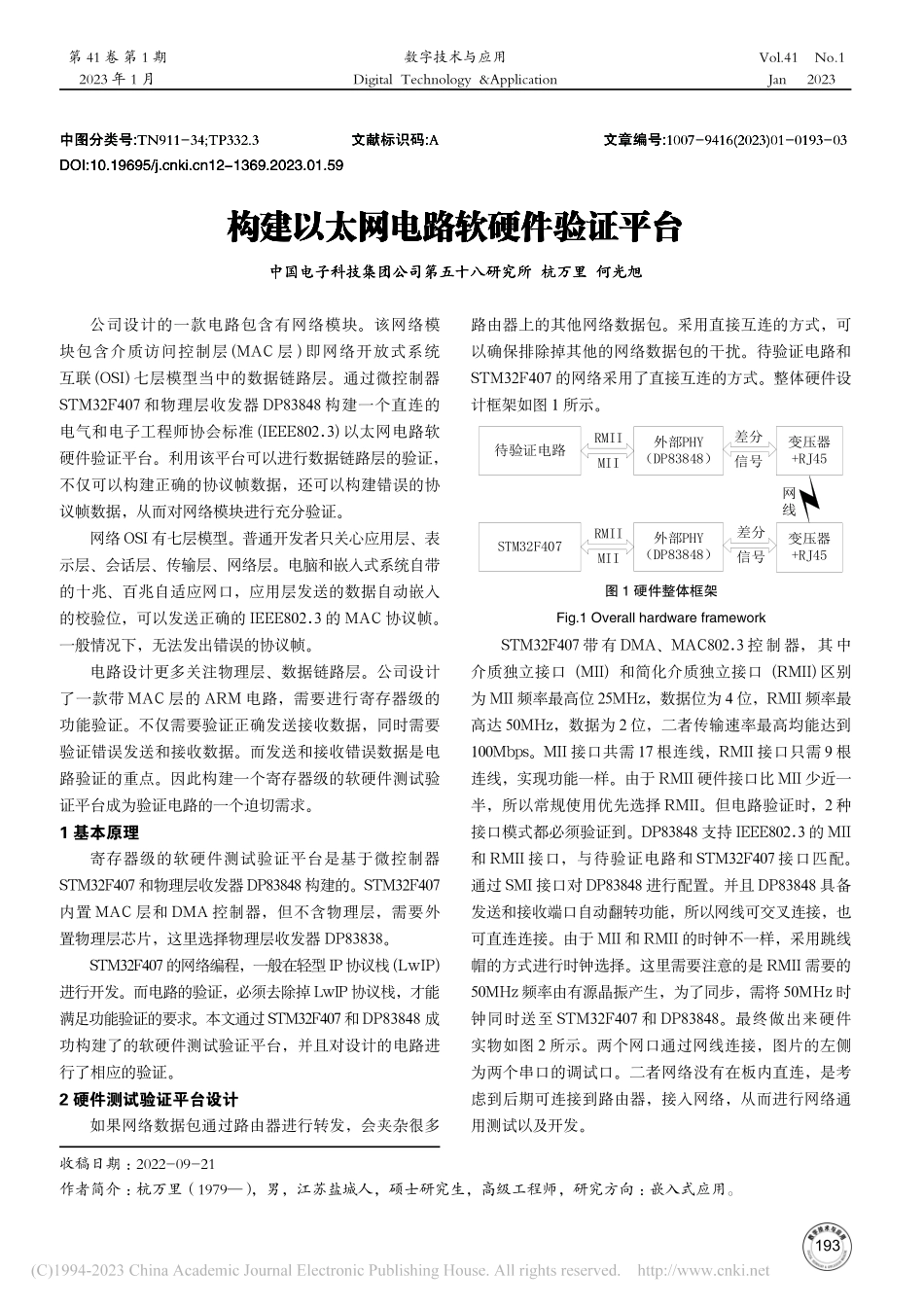

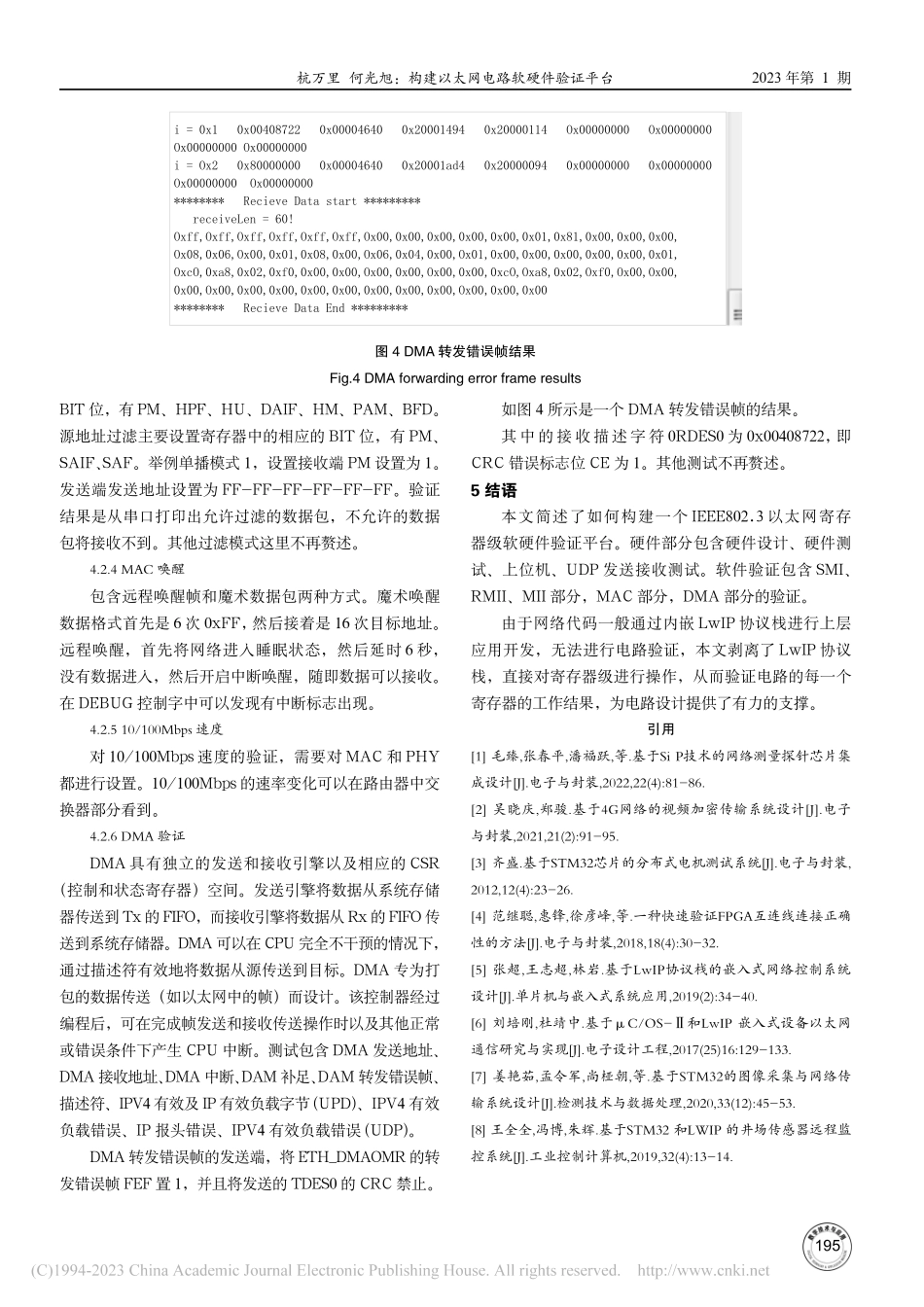

2023年1月Jan2023DigitalTechnology&Application第41卷第1期Vol.41No.1数字技术与应用193中图分类号:TN911-34;TP332.3文献标识码:A文章编号:1007-9416(2023)01-0193-03DOI:10.19695/j.cnki.cn12-1369.2023.01.59构建以太网电路软硬件验证平台中国电子科技集团公司第五十八研究所杭万里何光旭公司设计的一款电路包含有网络模块。该网络模块包含介质访问控制层(MAC层)即网络开放式系统互联(OSI)七层模型当中的数据链路层。通过微控制器STM32F407和物理层收发器DP83848构建一个直连的电气和电子工程师协会标准(IEEE802.3)以太网电路软硬件验证平台。利用该平台可以进行数据链路层的验证,不仅可以构建正确的协议帧数据,还可以构建错误的协议帧数据,从而对网络模块进行充分验证。网络OSI有七层模型。普通开发者只关心应用层、表示层、会话层、传输层、网络层。电脑和嵌入式系统自带的十兆、百兆自适应网口,应用层发送的数据自动嵌入的校验位,可以发送正确的IEEE802.3的MAC协议帧。一般情况下,无法发出错误的协议帧。电路设计更多关注物理层、数据链路层。公司设计了一款带MAC层的ARM电路,需要进行寄存器级的功能验证。不仅需要验证正确发送接收数据,同时需要验证错误发送和接收数据。而发送和接收错误数据是电路验证的重点。因此构建一个寄存器级的软硬件测试验证平台成为验证电路的一个迫切需求。1基本原理寄存器级的软硬件测试验证平台是基于微控制器STM32F407和物理层收发器DP83848构建的。STM32F407内置MAC层和DMA控制器,但不含物理层,需要外置物理层芯片,这里选择物理层收发器DP83838。STM32F407的网络编程,一般在轻型IP协议栈(LwIP)进行开发。而电路的验证,必须去除掉LwIP协议栈,才能满足功能验证的要求。本文通过STM32F407和DP83848成功构建了的软硬件测试验证平台,并且对设计的电路进行了相应的验证。2硬件测试验证平台设计如果网络数据包通过路由器进行转发,会夹杂很多路由器上的其他网络数据包。采用直接互连的方式,可以确保排除掉其他的网络数据包的干扰。待验证电路和STM32F407的网络采用了直接互连的方式。整体硬件设计框架如图1所示。待验证电路外部PHY(DP83848)变压器+RJ45STM32F407外部PHY(DP83848)变压器+RJ45网线RMIIMIIRMIIMII差分信号差分信号图1硬件整体框架Fig.1OverallhardwareframeworkSTM32F407带有DMA、MAC802.3控制器,其中介质独立接口(MII)和简化介质独立接口(RMII)区别为MII频率最高位25MHz,数据位...