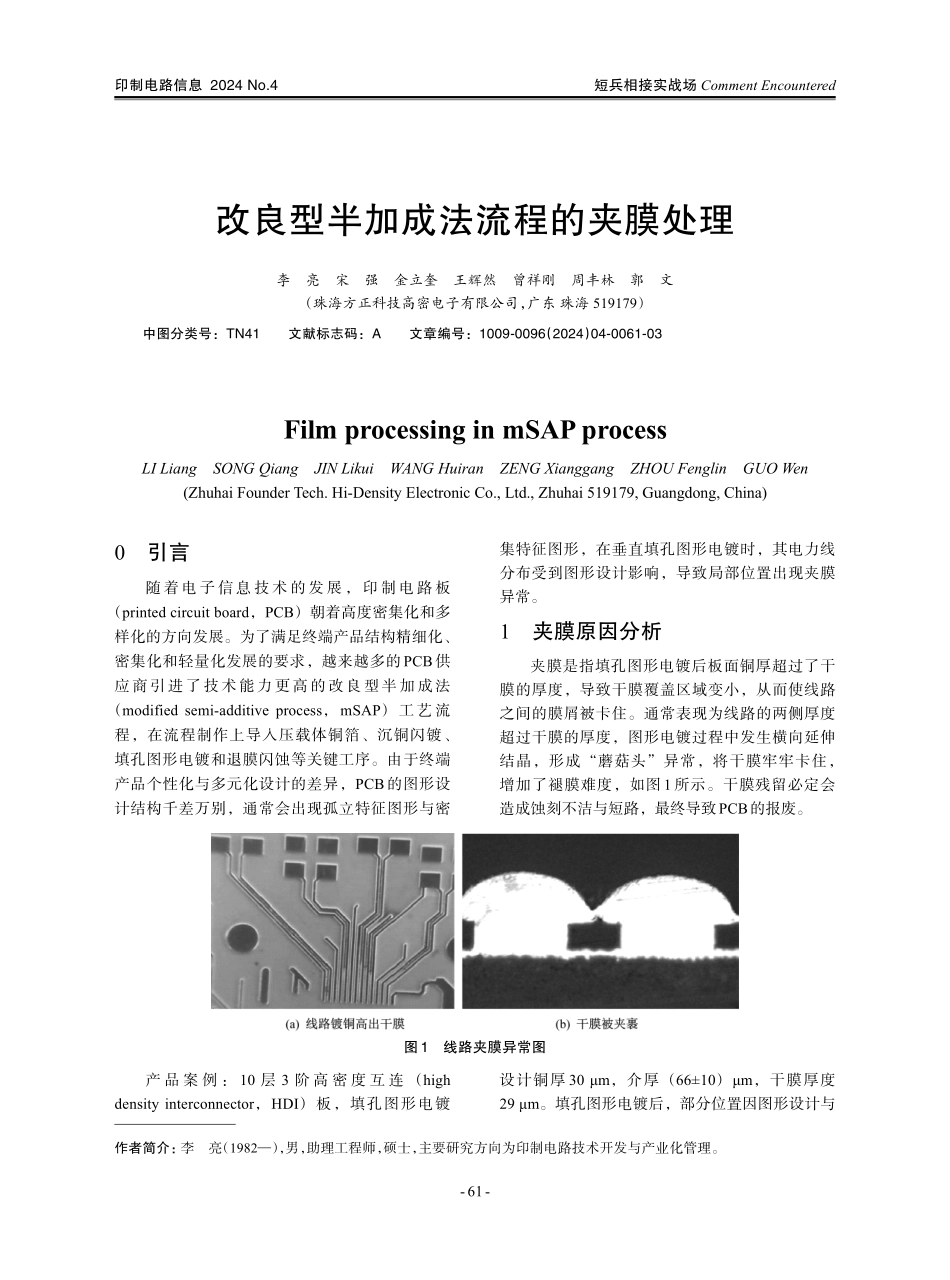

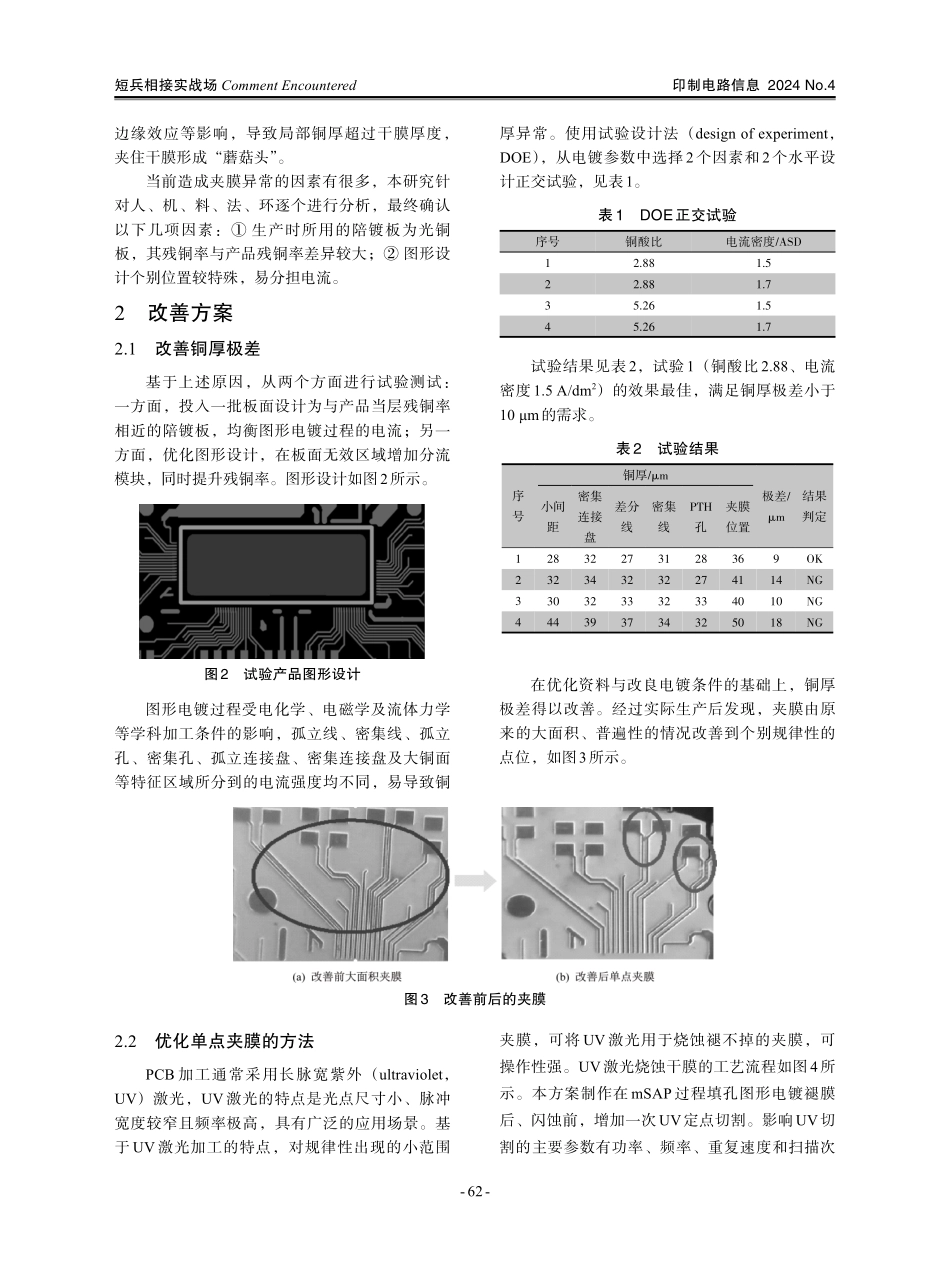

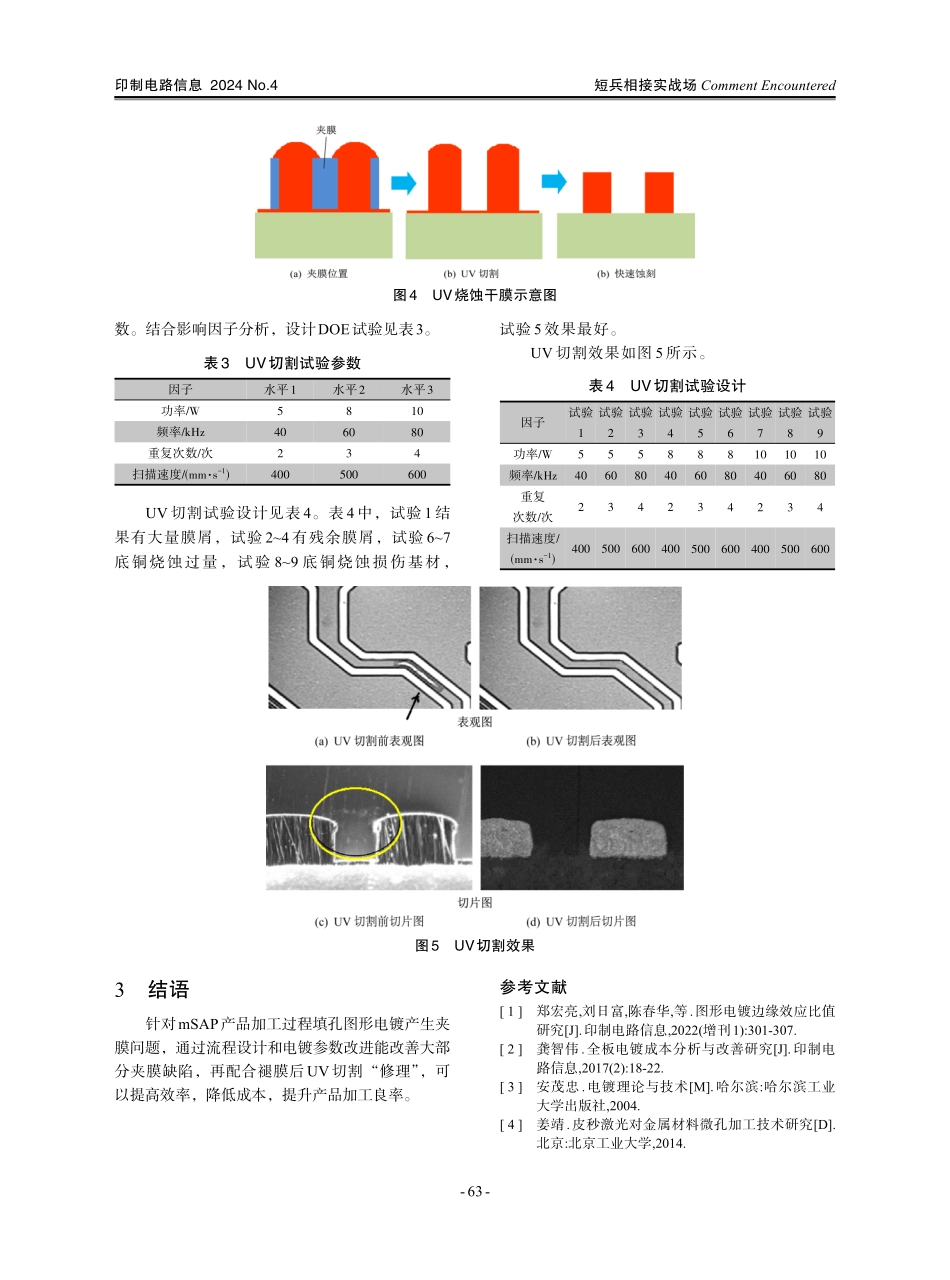

印制电路信息2024No.4短兵相接实战场CommentEncountered改良型半加成法流程的夹膜处理李亮宋强金立奎王辉然曾祥刚周丰林郭文(珠海方正科技高密电子有限公司,广东珠海519179)中图分类号:TN41文献标志码:A文章编号:1009⁃0096(2024)04⁃0061⁃03FilmprocessinginmSAPprocessLILiangSONGQiangJINLikuiWANGHuiranZENGXianggangZHOUFenglinGUOWen(ZhuhaiFounderTech.Hi-DensityElectronicCo.,Ltd.,Zhuhai519179,Guangdong,China)0引言随着电子信息技术的发展,印制电路板(printedcircuitboard,PCB)朝着高度密集化和多样化的方向发展。为了满足终端产品结构精细化、密集化和轻量化发展的要求,越来越多的PCB供应商引进了技术能力更高的改良型半加成法(modifiedsemi-additiveprocess,mSAP)工艺流程,在流程制作上导入压载体铜箔、沉铜闪镀、填孔图形电镀和退膜闪蚀等关键工序。由于终端产品个性化与多元化设计的差异,PCB的图形设计结构千差万别,通常会出现孤立特征图形与密集特征图形,在垂直填孔图形电镀时,其电力线分布受到图形设计影响,导致局部位置出现夹膜异常。1夹膜原因分析夹膜是指填孔图形电镀后板面铜厚超过了干膜的厚度,导致干膜覆盖区域变小,从而使线路之间的膜屑被卡住。通常表现为线路的两侧厚度超过干膜的厚度,图形电镀过程中发生横向延伸结晶,形成“蘑菇头”异常,将干膜牢牢卡住,增加了褪膜难度,如图1所示。干膜残留必定会造成蚀刻不洁与短路,最终导致PCB的报废。产品案例:10层3阶高密度互连(highdensityinterconnector,HDI)板,填孔图形电镀设计铜厚30μm,介厚(66±10)μm,干膜厚度29μm。填孔图形电镀后,部分位置因图形设计与图1线路夹膜异常图作者简介:李亮(1982—),男,助理工程师,硕士,主要研究方向为印制电路技术开发与产业化管理。--61短兵相接实战场CommentEncountered印制电路信息2024No.4边缘效应等影响,导致局部铜厚超过干膜厚度,夹住干膜形成“蘑菇头”。当前造成夹膜异常的因素有很多,本研究针对人、机、料、法、环逐个进行分析,最终确认以下几项因素:①生产时所用的陪镀板为光铜板,其残铜率与产品残铜率差异较大;②图形设计个别位置较特殊,易分担电流。2改善方案2.1改善铜厚极差基于上述原因,从两个方面进行试验测试:一方面,投入一批板面设计为与产品当层残铜率相近的陪镀板,均衡图形电镀过程的电流;另一方面,优化图形设计,在板面无效区域增加分流模块,同时提升...