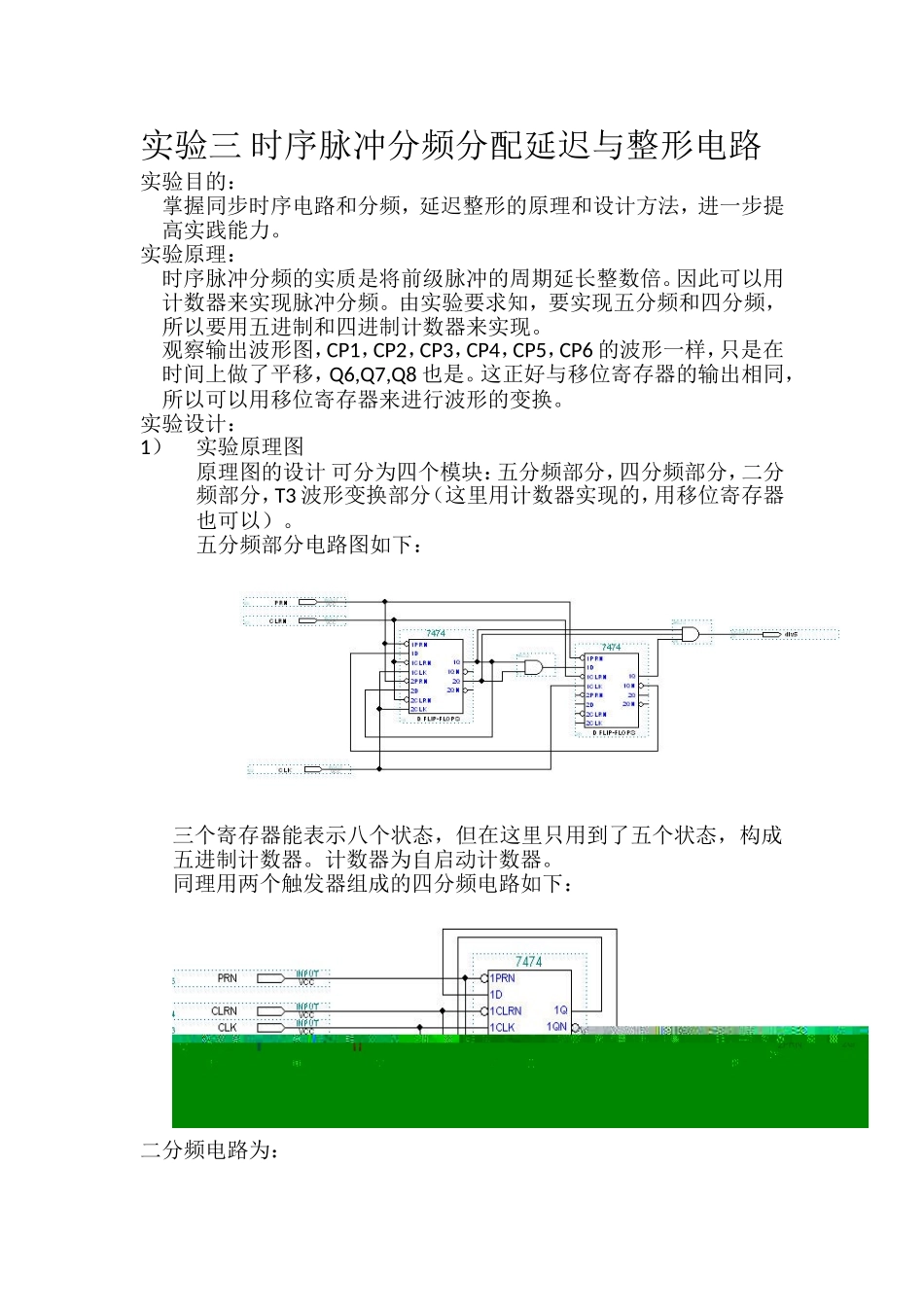

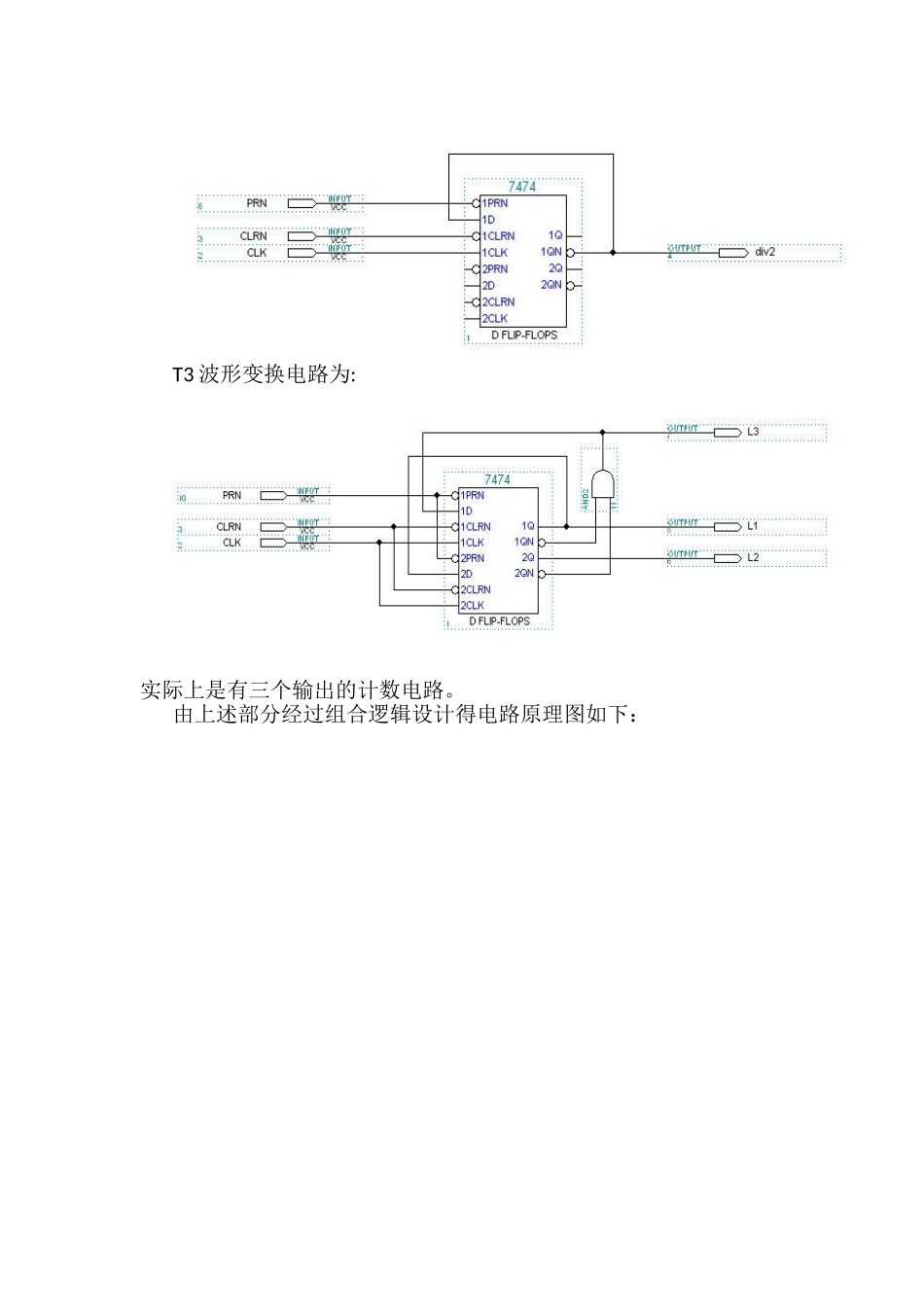

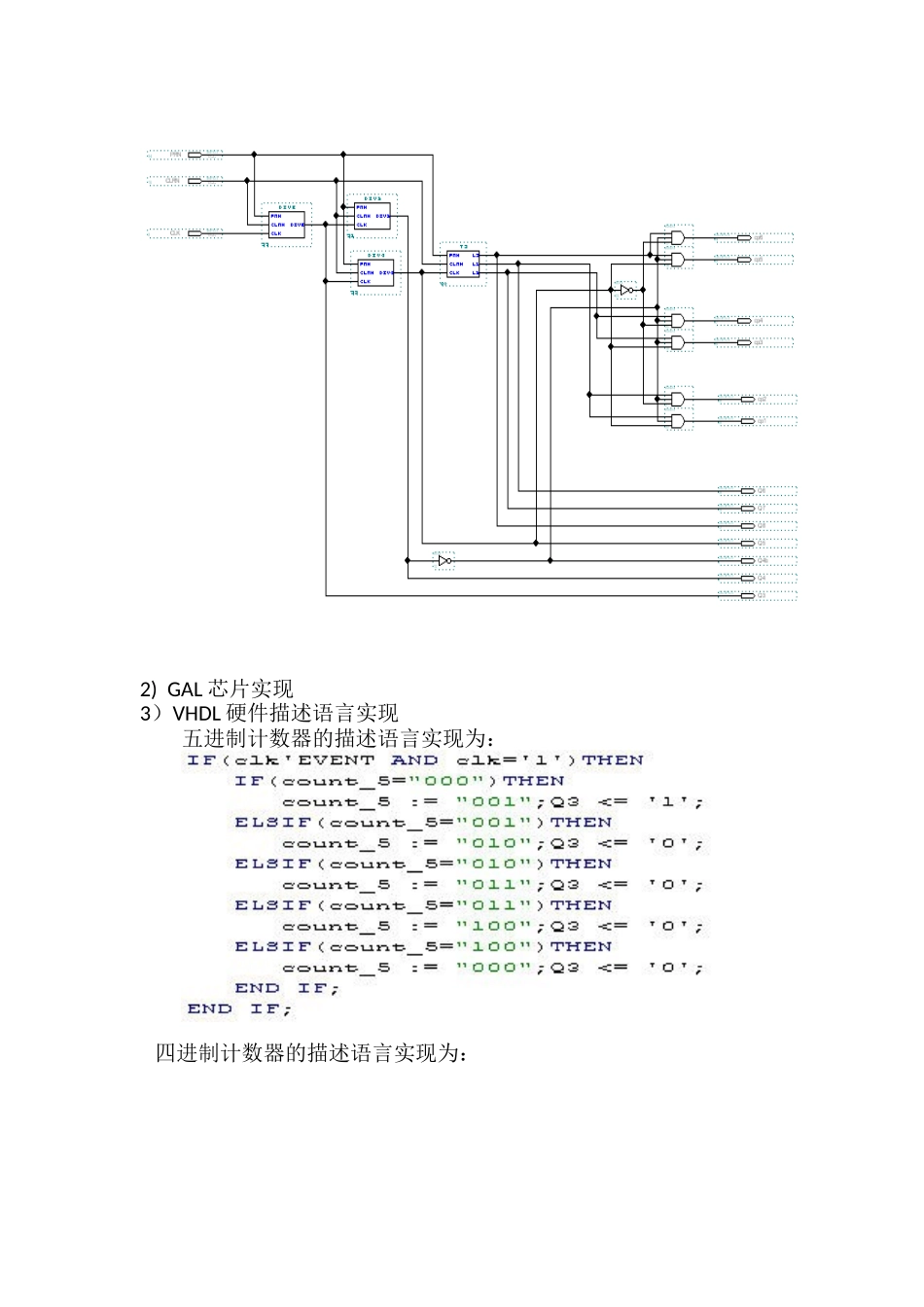

实验三时序脉冲分频分配延迟与整形电路实验目的:掌握同步时序电路和分频,延迟整形的原理和设计方法,进一步提高实践能力。实验原理:时序脉冲分频的实质是将前级脉冲的周期延长整数倍。因此可以用计数器来实现脉冲分频。由实验要求知,要实现五分频和四分频,所以要用五进制和四进制计数器来实现。观察输出波形图,CP1,CP2,CP3,CP4,CP5,CP6的波形一样,只是在时间上做了平移,Q6,Q7,Q8也是。这正好与移位寄存器的输出相同,所以可以用移位寄存器来进行波形的变换。实验设计:1)实验原理图原理图的设计可分为四个模块:五分频部分,四分频部分,二分频部分,T3波形变换部分(这里用计数器实现的,用移位寄存器也可以)。五分频部分电路图如下:三个寄存器能表示八个状态,但在这里只用到了五个状态,构成五进制计数器。计数器为自启动计数器。同理用两个触发器组成的四分频电路如下:二分频电路为:T3波形变换电路为:实际上是有三个输出的计数电路。由上述部分经过组合逻辑设计得电路原理图如下:2)GAL芯片实现3)VHDL硬件描述语言实现五进制计数器的描述语言实现为:四进制计数器的描述语言实现为:同理,二进制计数器的描述语言实现为:所以,将原理图的实现用VHDL语言描述为:LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYclkISPORT(clk:INSTD_LOGIC;CP1,CP2,CP3,CP4,CP5,CP6:OUTSTD_LOGIC;Q3,Q4,Q4b,Q5,Q6,Q7,Q8:BUFFERSTD_LOGIC);ENDclk;ARCHITECTUREVHDLOFclkISBEGINPROCESS(clk,Q3,Q5)VARIABLEcount_5:STD_LOGIC_VECTOR(2DOWNTO0);VARIABLEcount_2:STD_LOGIC;VARIABLEcount_4:STD_LOGIC_VECTOR(1DOWNTO0);VARIABLEcount_3:STD_LOGIC_VECTOR(1DOWNTO0);BEGINIF(clk'EVENTANDclk='1')THENIF(count_5="000")THENcount_5:="001";Q3<='1';ELSIF(count_5="001")THENcount_5:="010";Q3<='0';ELSIF(count_5="010")THENcount_5:="011";Q3<='0';ELSIF(count_5="011")THENcount_5:="100";Q3<='0';ELSIF(count_5="100")THENcount_5:="000";Q3<='0';ENDIF;ENDIF;IF(Q3'EVENTANDQ3='1')THENIF(count_2='0')THENcount_2:='1';Q4<='1';Q4b<='0';ELSIF(count_2='1')THENcount_2:='0';Q4<='0';Q4b<='1';ENDIF;ENDIF;IF(Q3'EVENTANDQ3='1')THENIF(count_4="00")THENcount_4:="01";Q5<='1';ELSIF(count_4="01")THENcount_4:="10";Q5<='1';ELSIF(count_4="10")THENcount_4:="11";Q5<='0';ELSIF(count_4="11")THENcount_4:="00";Q5<='0';ENDIF;ENDIF;IF(Q...