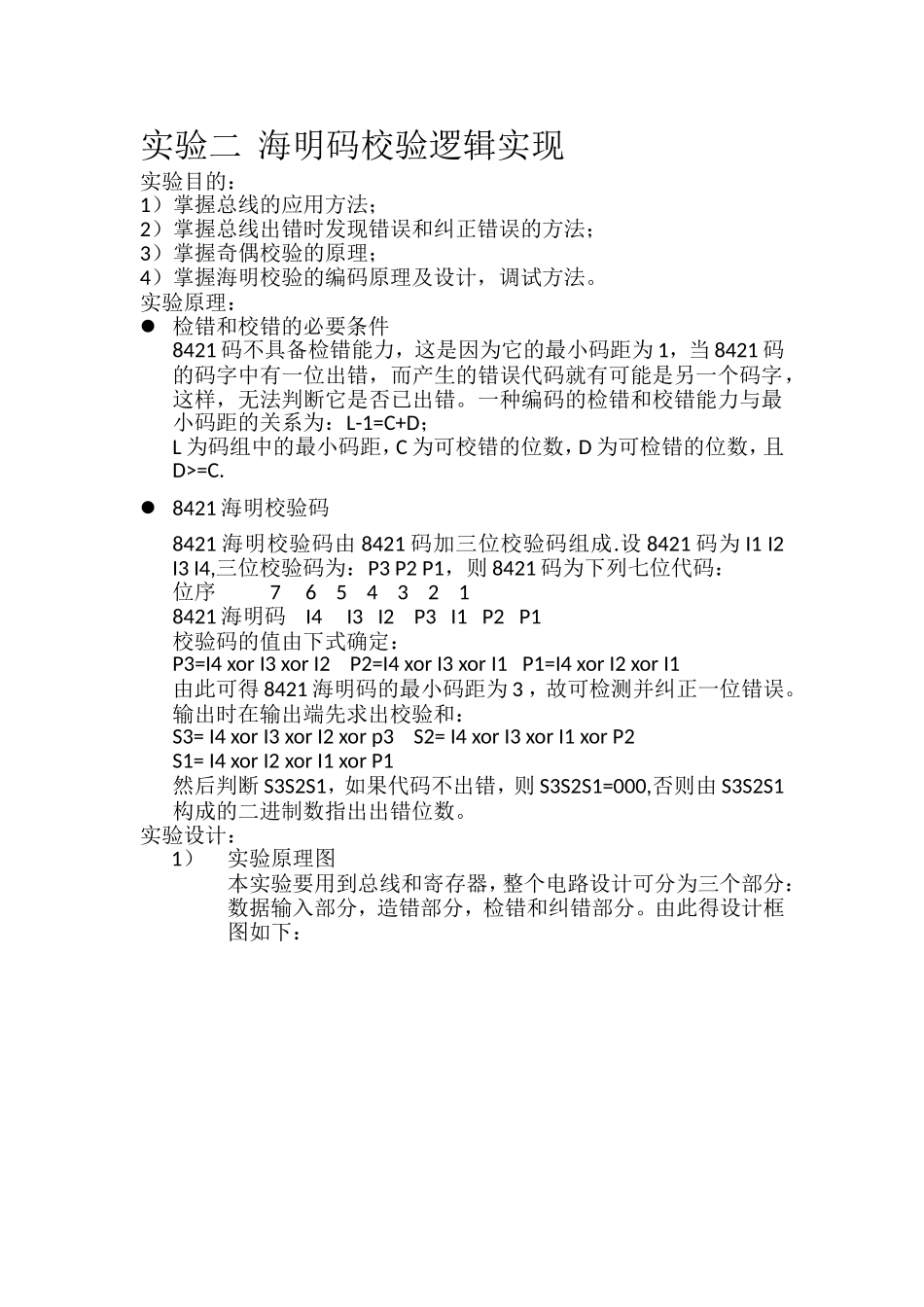

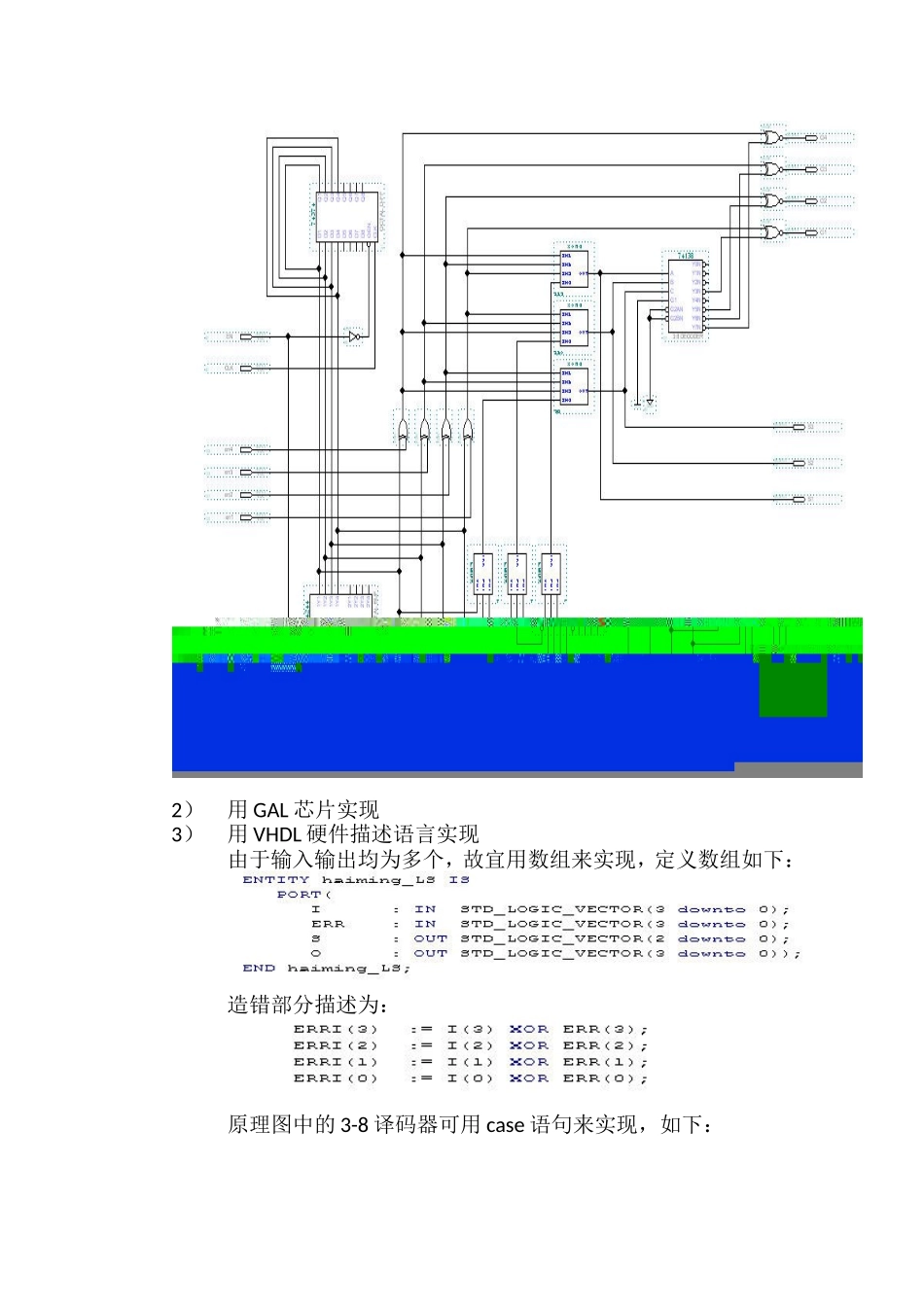

实验二海明码校验逻辑实现实验目的:1)掌握总线的应用方法;2)掌握总线出错时发现错误和纠正错误的方法;3)掌握奇偶校验的原理;4)掌握海明校验的编码原理及设计,调试方法。实验原理:检错和校错的必要条件8421码不具备检错能力,这是因为它的最小码距为1,当8421码的码字中有一位出错,而产生的错误代码就有可能是另一个码字,这样,无法判断它是否已出错。一种编码的检错和校错能力与最小码距的关系为:L-1=C+D;L为码组中的最小码距,C为可校错的位数,D为可检错的位数,且D>=C.8421海明校验码8421海明校验码由8421码加三位校验码组成.设8421码为I1I2I3I4,三位校验码为:P3P2P1,则8421码为下列七位代码:位序76543218421海明码I4I3I2P3I1P2P1校验码的值由下式确定:P3=I4xorI3xorI2P2=I4xorI3xorI1P1=I4xorI2xorI1由此可得8421海明码的最小码距为3,故可检测并纠正一位错误。输出时在输出端先求出校验和:S3=I4xorI3xorI2xorp3S2=I4xorI3xorI1xorP2S1=I4xorI2xorI1xorP1然后判断S3S2S1,如果代码不出错,则S3S2S1=000,否则由S3S2S1构成的二进制数指出出错位数。实验设计:1)实验原理图本实验要用到总线和寄存器,整个电路设计可分为三个部分:数据输入部分,造错部分,检错和纠错部分。由此得设计框图如下:考察异或门的输入输出特性知,一位输入恒为高电平时可对另一位进行造错,由于只需对四位信息为造错,故可用一对一法进行造错是电路简单。由上分析,得电路原理图如下:2)用GAL芯片实现3)用VHDL硬件描述语言实现由于输入输出均为多个,故宜用数组来实现,定义数组如下:造错部分描述为:原理图中的3-8译码器可用case语句来实现,如下:最后纠错为:O<=ERRIXORYIMA;VHDL描述如下:实验波形图如下:实验小结:这次实验主要是建立起了总线和使能控制的概念,和实验一相比,本实验中引入了时序逻辑(寄存器)。虽然实验原理不难,但由于是初次使用MAX+plus,所以这次实验花的时间比较多,特别是用原理图实现部分。通过这次实验,对寄存器和总线结构有了更进一步的理解,同时也学会了MAX+plus的初步使用,对异或门和同或门的输入输出特性也有了更深的了解。