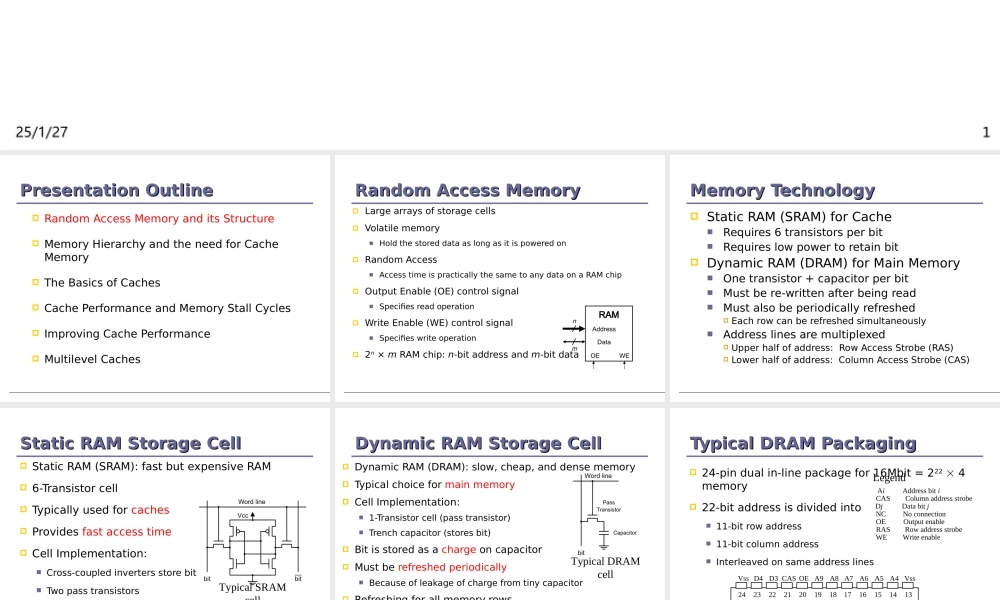

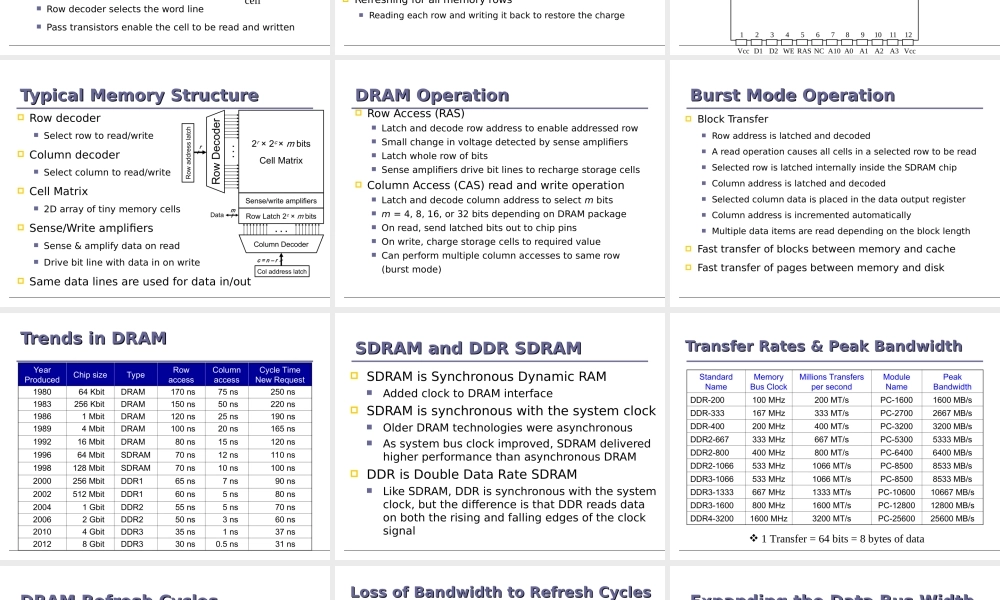

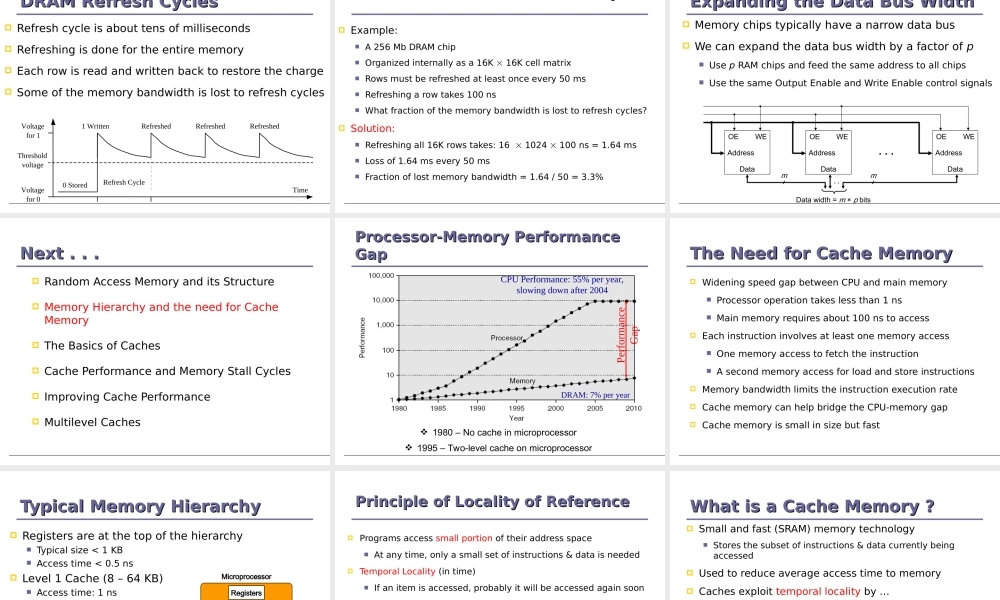

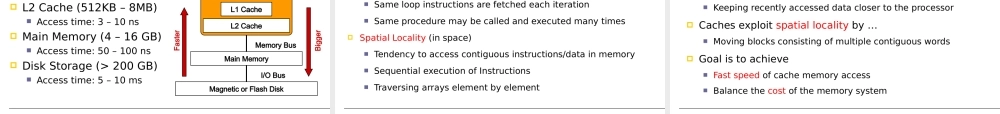

ComputerComputerOrganization&DesignOrganization&Design——TheHardware/SoftwareInterfaceTheHardware/SoftwareInterface25/1/271PresentationOutlinePresentationOutlineRandomAccessMemoryanditsStructureMemoryHierarchyandtheneedforCacheMemoryTheBasicsofCachesCachePerformanceandMemoryStallCyclesImprovingCachePerformanceMultilevelCachesLargearraysofstoragecellsVolatilememoryHoldthestoreddataaslongasitispoweredonRandomAccessAccesstimeispracticallythesametoanydataonaRAMchipOutputEnable(OE)controlsignalSpecifiesreadoperationWriteEnable(WE)controlsignalSpecifieswriteoperation2n×mRAMchip:n-bitaddressandm-bitdataRandomAccessMemoryRandomAccessMemoryRAMAddressDataOEWEnmMemoryTechnologyMemoryTechnologyStaticRAM(SRAM)forCacheRequires6transistorsperbitRequireslowpowertoretainbitDynamicRAM(DRAM)forMainMemoryOnetransistor+capacitorperbitMustbere-writtenafterbeingreadMustalsobeperiodicallyrefreshedEachrowcanberefreshedsimultaneouslyAddresslinesaremultiplexedUpperhalfofaddress:RowAccessStrobe(RAS)Lowerhalfofaddress:ColumnAccessStrobe(CAS)StaticRAMStorageCellStaticRAMStorageCellStaticRAM(SRAM):fastbutexpensiveRAM6-TransistorcellTypicallyusedforcachesProvidesfastaccesstimeCellImplementation:Cross-coupledinvertersstorebitTwopasstransistorsRowdecoderselectsthewordlinePasstransistorsenablethecelltobereadandwrittenTypicalSRAMcellVccWordlinebitbitDynamicRAMStorageCellDynamicRAMStorageCellDynamicRAM(DRAM):slow,cheap,anddensememoryTypicalchoiceformainmemoryCellImplementation:1-Transistorcell(passtransistor)Trenchcapacitor(storesbit)BitisstoredasachargeoncapacitorMustberefreshedperiodicallyBecauseofleakageofchargefromtinycapacitorRefreshingforallmemoryrowsReadingeachrowandwritingitbacktorestorethechargeTypicalDRAMcellWordlinebitCapacitorPassTransistorTypicalDRAMPackagingTypicalDRAMPackaging24-pindualin-linepackagefor16Mbit=2224memory22-bitaddressisdividedinto11-bitrowaddress11-bitcolumnaddressI...