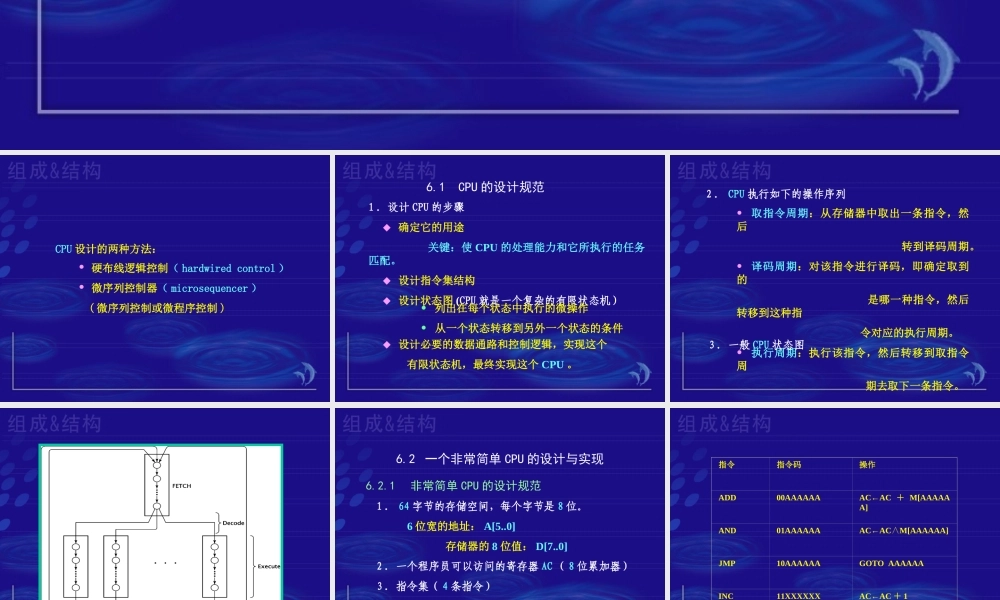

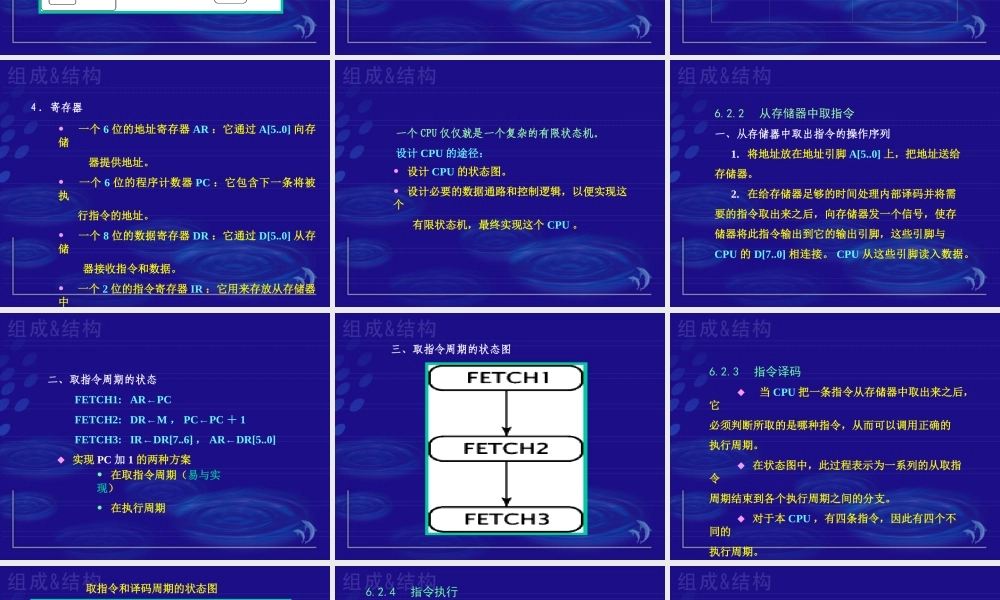

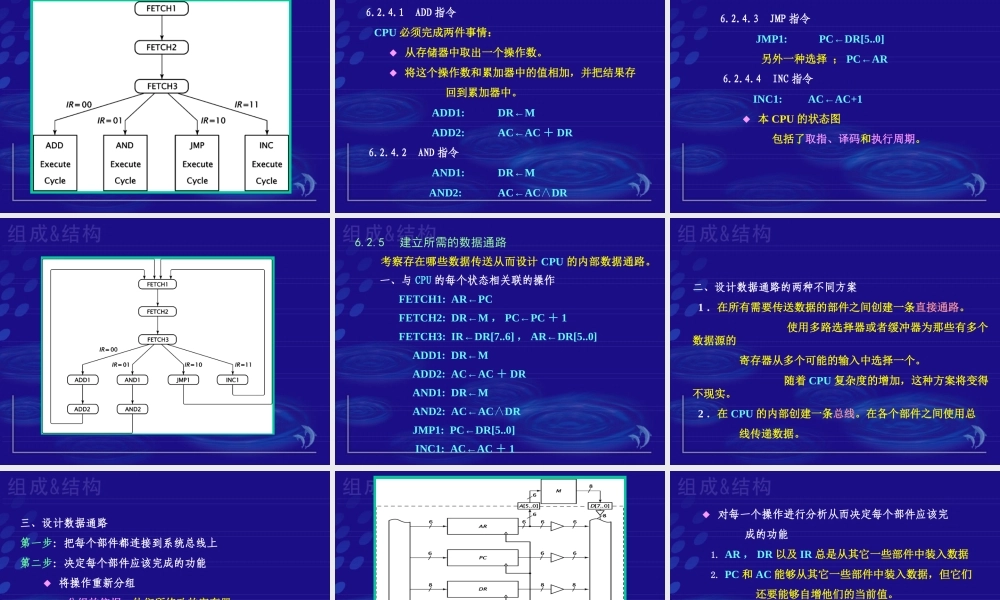

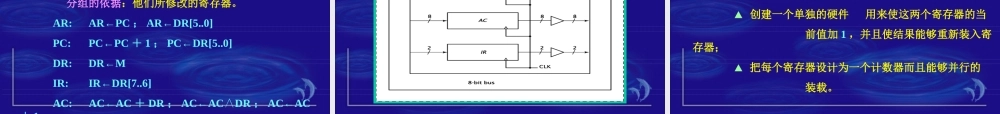

6.1CPU的设计规范6.2一个非常简单CPU的设计与实现6.3相对简单CPU的设计和实现6.4简单CPU的缺点6.5实例:8085微处理器的内部结构第六章CPU设计CPU设计的两种方法:•硬布线逻辑控制(hardwiredcontrol)•微序列控制器(microsequencer)(微序列控制或微程序控制)6.1CPU的设计规范1.设计CPU的步骤◆确定它的用途关键:使CPU的处理能力和它所执行的任务匹配。◆设计指令集结构◆设计状态图(CPU就是一个复杂的有限状态机)•列出在每个状态中执行的微操作•从一个状态转移到另外一个状态的条件◆设计必要的数据通路和控制逻辑,实现这个有限状态机,最终实现这个CPU。2.CPU执行如下的操作序列•取指令周期:从存储器中取出一条指令,然后转到译码周期。•译码周期:对该指令进行译码,即确定取到的是哪一种指令,然后转移到这种指令对应的执行周期。•执行周期:执行该指令,然后转移到取指令周期去取下一条指令。3.一般CPU状态图6.2.1非常简单CPU的设计规范1.64字节的存储空间,每个字节是8位。6位宽的地址:A[5..0]存储器的8位值:D[7..0]2.一个程序员可以访问的寄存器AC(8位累加器)3.指令集(4条指令)6.2一个非常简单CPU的设计与实现指令指令码操作ADD00AAAAAAAC←AC+M[AAAAAA]AND01AAAAAAAC←ACM[AAAAAA]∧JMP10AAAAAAGOTOAAAAAAINC11XXXXXXAC←AC+14.寄存器•一个6位的地址寄存器AR:它通过A[5..0]向存储器提供地址。•一个6位的程序计数器PC:它包含下一条将被执行指令的地址。•一个8位的数据寄存器DR:它通过D[5..0]从存储器接收指令和数据。•一个2位的指令寄存器IR:它用来存放从存储器中一个CPU仅仅就是一个复杂的有限状态机。设计CPU的途径:•设计CPU的状态图。•设计必要的数据通路和控制逻辑,以便实现这个有限状态机,最终实现这个CPU。6.2.2从存储器中取指令一、从存储器中取出指令的操作序列1.将地址放在地址引脚A[5..0]上,把地址送给存储器。2.在给存储器足够的时间处理内部译码并将需要的指令取出来之后,向存储器发一个信号,使存储器将此指令输出到它的输出引脚,这些引脚与CPU的D[7..0]相连接。CPU从这些引脚读入数据。二、取指令周期的状态FETCH1:AR←PCFETCH2:DR←M,PC←PC+1FETCH3:IR←DR[7..6],AR←DR[5..0]◆实现PC加1的两种方案•在取指令周期(易与实现)•在执行周期三、取指令周期的状态图6.2.3指令译码◆当CPU把一条指令从存储器中取出来之后,它必须判断所取的是哪种指令,从而可以调用正确的执行周...