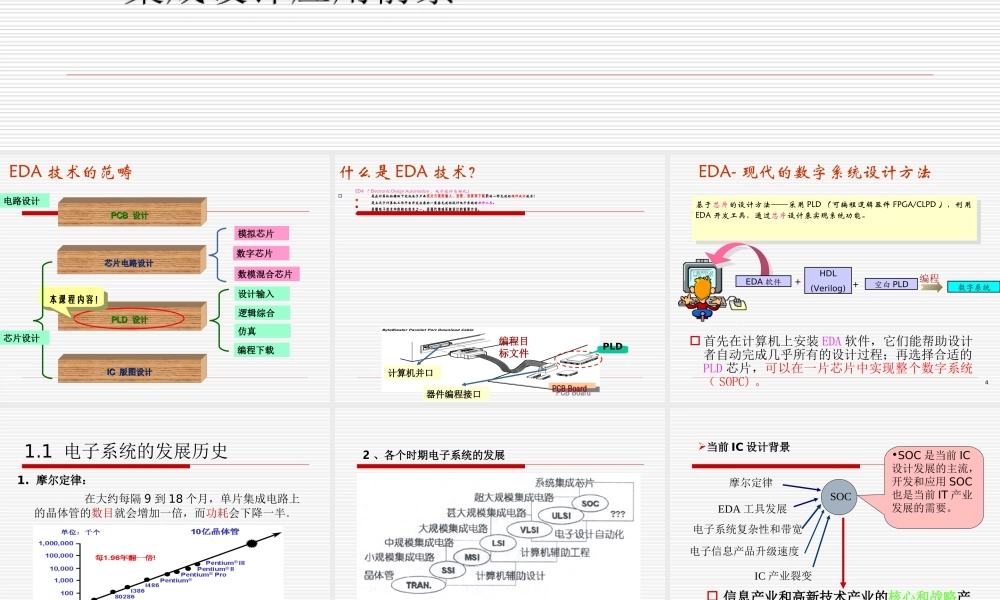

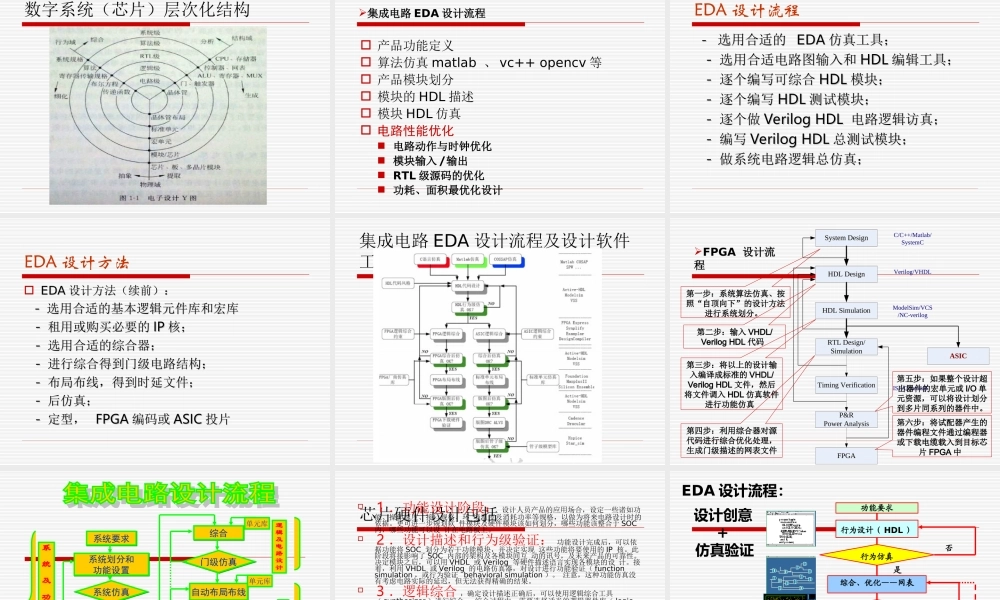

第1章集成电路EDA设计概述本课程中EDA定义电子系统发展历史高性能集成化设计数字集成化设计流程数字系统实现方法集成化设计发展趋势集成设计应用前景EDA技术的范畴ICIC版图设计版图设计PLDPLD设计设计芯片电路设计芯片电路设计PCBPCB设计设计模拟芯片数字芯片数模混合芯片设计输入逻辑综合仿真编程下载本课程内容!本课程内容!芯片设计电路设计什么是EDA技术?EDA(ElectronicDesignAutomation,电子设计自动化)是在计算机的辅助下完成电子产品设计方案的输入、处理、仿真和下载的的一种先进的硬件设计技术!是立足于计算机工作平台开发出来的一整套先进的设计电子系统的软件工具。是微电子技术中的核心技术之一,是现代集成系统设计的重要方法。计算机并口器件编程接口PCBBoardPCBBoardPLDPLD编程目标文件4EDA-现代的数字系统设计方法首先在计算机上安装EDA软件,它们能帮助设计者自动完成几乎所有的设计过程;再选择合适的PLD芯片,可以在一片芯片中实现整个数字系统(SOPC)。基于芯片的设计方法——采用PLD(可编程逻辑器件FPGA/CLPD),利用EDA开发工具,通过芯片设计来实现系统功能。基于芯片的设计方法——采用PLD(可编程逻辑器件FPGA/CLPD),利用EDA开发工具,通过芯片设计来实现系统功能。EDA软件空白PLD+数字系统编程+HDL(Verilog)1.摩尔定律:在大约每隔9到18个月,单片集成电路上的晶体管的数目就会增加一倍,而功耗会下降一半。1.1电子系统的发展历史2、各个时期电子系统的发展当前IC设计背景信息产业和高新技术产业的核心和战略产业是集成电路产业。摩尔定律EDA工具发展SOC电子系统复杂性和带宽电子信息产品升级速度•SOC是当前IC设计发展的主流,开发和应用SOC也是当前IT产业发展的需要。IC产业裂变3、现代硬件电路的设计现状数字集成电路DSPFPGASOCNOC4.数字系统的热门方向:1.2高性能集成化设计大规模集成化带来自动设计的进步(EDA)。电路、工作的复杂化带来HDL的普及。C/C++与HDL差别4004,几千门级486,几百万门级Core2,几亿门级现代技术快速发展使得综合性学科的出现速度:系统的速度是由系统的时序和时滞两个因素决定主要主要物理物理特性特性吞吐量:即是数据流量,即每个时钟内处理的数据量面积:是通过半导体工艺不断研发实现低面积消耗功耗:随着集成度的增加,单位面积上的晶体管数目增加,降低功耗是必然数字集成化系统的性能的主要4个特性1.3数字集成化设计流...