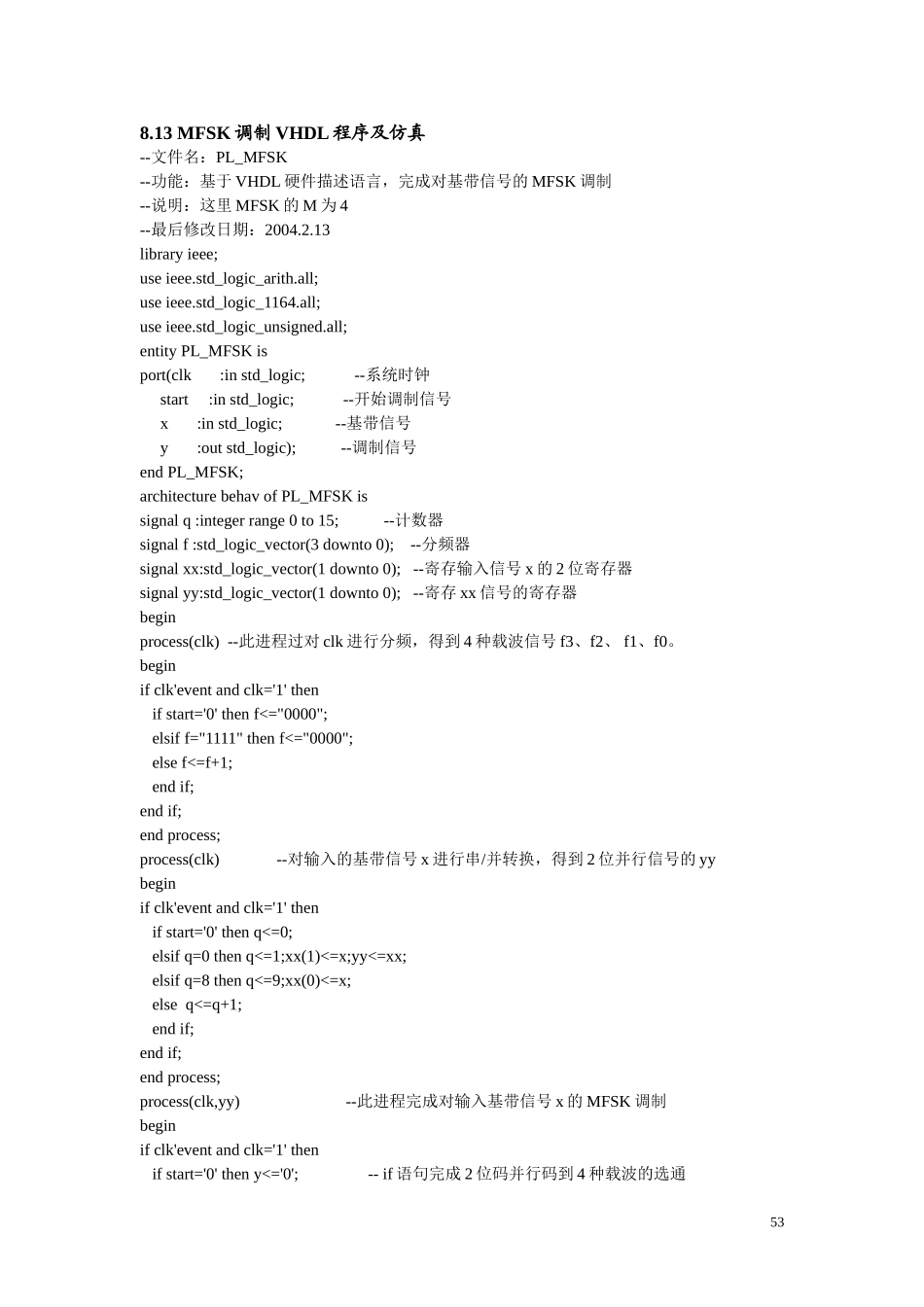

8.13MFSK调制VHDL程序及仿真--文件名:PL_MFSK--功能:基于VHDL硬件描述语言,完成对基带信号的MFSK调制--说明:这里MFSK的M为4--最后修改日期:2004.2.13libraryieee;useieee.std_logic_arith.all;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entityPL_MFSKisport(clk:instd_logic;--系统时钟start:instd_logic;--开始调制信号x:instd_logic;--基带信号y:outstd_logic);--调制信号endPL_MFSK;architecturebehavofPL_MFSKissignalq:integerrange0to15;--计数器signalf:std_logic_vector(3downto0);--分频器signalxx:std_logic_vector(1downto0);--寄存输入信号x的2位寄存器signalyy:std_logic_vector(1downto0);--寄存xx信号的寄存器beginprocess(clk)--此进程过对clk进行分频,得到4种载波信号f3、f2、f1、f0。beginifclk'eventandclk='1'thenifstart='0'thenf<="0000";elsiff="1111"thenf<="0000";elsef<=f+1;endif;endif;endprocess;process(clk)--对输入的基带信号x进行串/并转换,得到2位并行信号的yybeginifclk'eventandclk='1'thenifstart='0'thenq<=0;elsifq=0thenq<=1;xx(1)<=x;yy<=xx;elsifq=8thenq<=9;xx(0)<=x;elseq<=q+1;endif;endif;endprocess;process(clk,yy)--此进程完成对输入基带信号x的MFSK调制beginifclk'eventandclk='1'thenifstart='0'theny<='0';--if语句完成2位码并行码到4种载波的选通53elsifyy="00"theny<=notf(3);elsifyy="01"theny<=notf(2);elsifyy="10"theny<=notf(1);elsey<=notf(0);endif;endif;endprocess;endbehav;3.MFSK调制VHDL程序仿真图及注释MFSK调制VHDL程序仿真图及注释如图8.13.4所示。(a)MFSK调制VHDL程序仿真全图注:中间信号yy与输出调制信号y的对应关系:“00”=f3;“01”=f2;“10”=f1;“11”=f0。(b)MFSK调制VHDL程序仿真局部放大图154(c)MFSK调制VHDL程序仿真局部放大图2(d)MFSK调制VHDL程序仿真局部放大图3图8.13.4MFSK调制VHDL程序仿真图及注释55