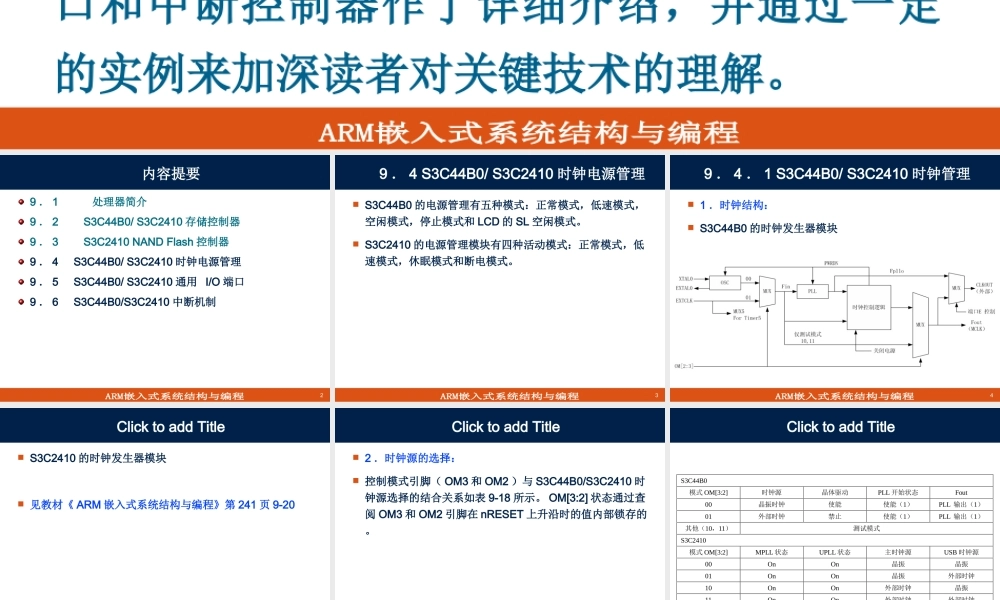

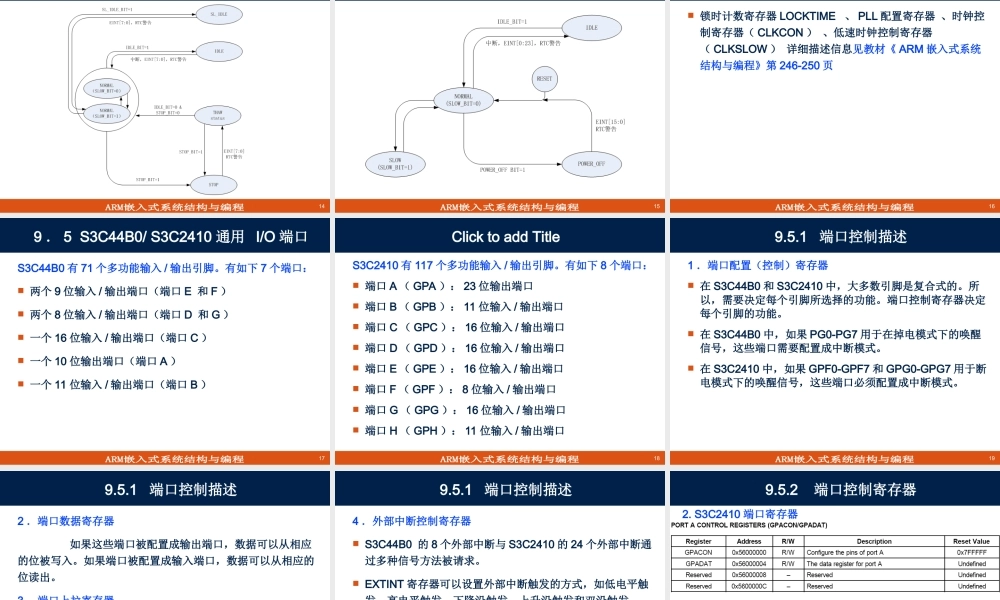

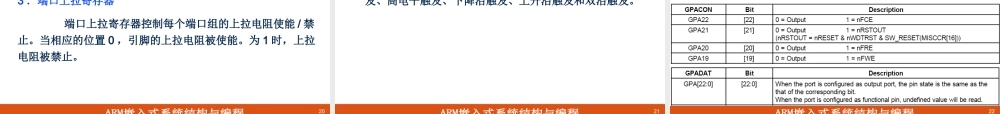

1TM第9章S3C44B0/S3C2410硬件结构与关键技术分析S3C44B0是基于ARM7TDMI架构的,S3C2410是基于ARM920T架构的。当前,这两款芯片在嵌入式开发领域广泛应用。本章主要介绍S3C44B0和S3C2410的硬件资源和整体架构,对其存储控制器、NANDFlash控制原理、时钟电源管理、通用I/O接口和中断控制器作了详细介绍,并通过一定的实例来加深读者对关键技术的理解。2TM2内容提要9.1处理器简介9.2S3C44B0/S3C2410存储控制器9.3S3C2410NANDFlash控制器9.4S3C44B0/S3C2410时钟电源管理9.5S3C44B0/S3C2410通用I/O端口9.6S3C44B0/S3C2410中断机制3TM39.4S3C44B0/S3C2410时钟电源管理S3C44B0的电源管理有五种模式:正常模式,低速模式,空闲模式,停止模式和LCD的SL空闲模式。S3C2410的电源管理模块有四种活动模式:正常模式,低速模式,休眠模式和断电模式。4TM49.4.1S3C44B0/S3C2410时钟管理1.时钟结构:S3C44B0的时钟发生器模块5TM5ClicktoaddTitleS3C2410的时钟发生器模块见教材《ARM嵌入式系统结构与编程》第241页9-206TM6ClicktoaddTitle2.时钟源的选择:控制模式引脚(OM3和OM2)与S3C44B0/S3C2410时钟源选择的结合关系如表9-18所示。OM[3:2]状态通过查阅OM3和OM2引脚在nRESET上升沿时的值内部锁存的。7TM7ClicktoaddTitleS3C44B0模式OM[3:2]时钟源晶体驱动PLL开始状态Fout00晶振时钟使能使能(1)PLL输出(1)01外部时钟禁止使能(1)PLL输出(1)其他(10,11)测试模式S3C2410模式OM[3:2]MPLL状态UPLL状态主时钟源USB时钟源00OnOn晶振晶振01OnOn晶振外部时钟10OnOn外部时钟晶振11OnOn外部时钟外部时钟8TM8ClicktoaddTitle3.PLL(锁相环)内置时钟发生器的S3C44B0PLL/S3C2410MPLL是一个以频率与相位输入信号的基准的同步输出信号的电路。9TM9ClicktoaddTitle4.上电复位:晶振开始振荡数毫秒后,当S3C44B0OSC(S3C2410:XTlpll)时钟稳定后nRESET得到释放,PLL开始根据默认的PLL配置进行运作。PLL在上电复位后变得不稳定,所以Fin代替Fpllo(S3C2410:Mpll)在S/W(S3C2410:软件)更新PLLCON的配置前直接反馈到Fout。用户在复位后想使用PLLCON寄存器的默认值,也需要通过S/W(S3C2410:软件)写入相同的值给PLLCON寄存器。10TM10上电复位时钟锁定11TM11ClicktoaddTitle在正常模式下的操作,如果用户希望通过写PMS值的方法改变频率,PLL锁定时间会自动写入。在锁定时间里,时钟不支持内部模块。12TM129.4.2S3C44B0/S3C...