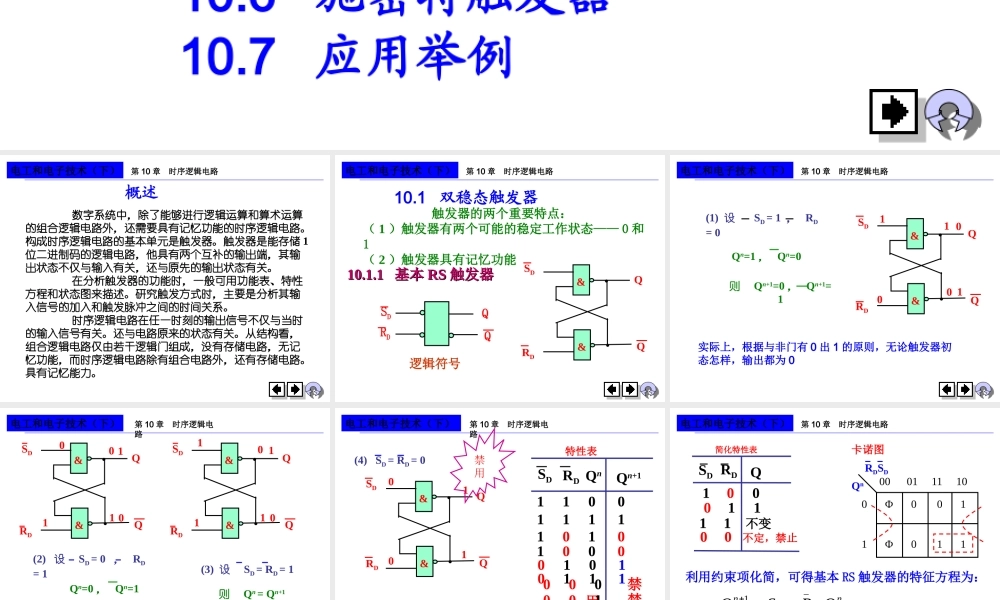

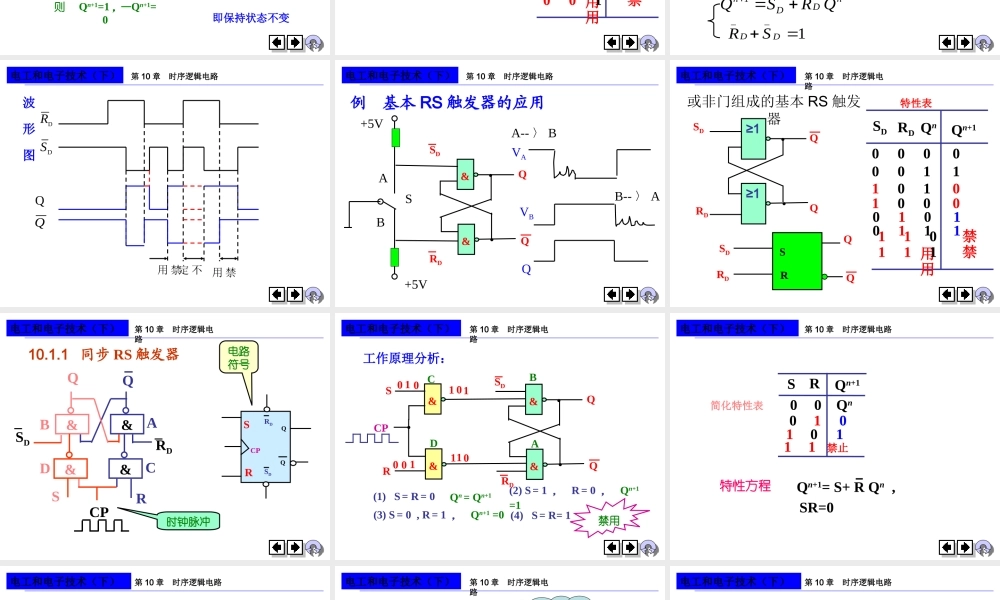

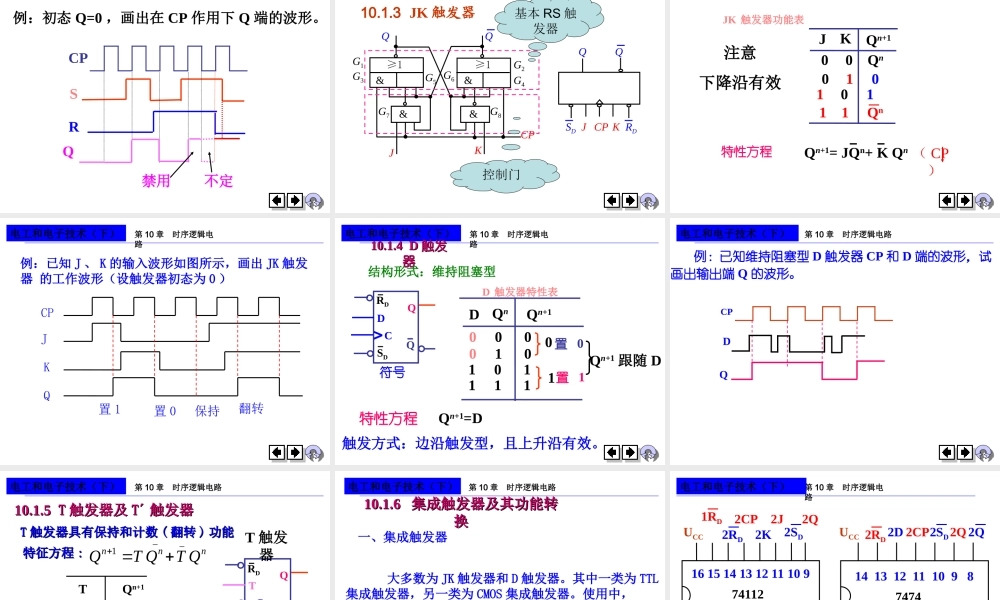

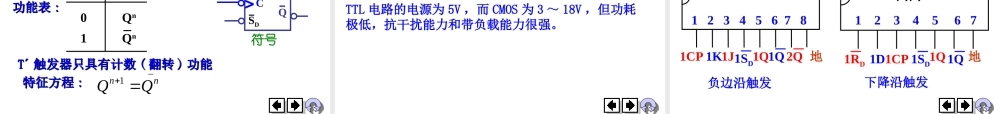

第10章时序逻辑电路电工和电子技术(下)第10章时序逻辑电路10.1双稳态触发器10.2寄存器10.3计数器10.4单稳态触发器10.5多谐振荡器10.6施密特触发器10.7应用举例第10章时序逻辑电路电工和电子技术(下)概述数字系统中,除了能够进行逻辑运算和算术运算的组合逻辑电路外,还需要具有记忆功能的时序逻辑电路。构成时序逻辑电路的基本单元是触发器。触发器是能存储1位二进制码的逻辑电路,他具有两个互补的输出端,其输出状态不仅与输入有关,还与原先的输出状态有关。在分析触发器的功能时,一般可用功能表、特性方程和状态图来描述。研究触发方式时,主要是分析其输入信号的加入和触发脉冲之间的时间关系。时序逻辑电路在任一时刻的输出信号不仅与当时的输入信号有关。还与电路原来的状态有关。从结构看,组合逻辑电路仅由若干逻辑门组成,没有存储电路,无记忆功能,而时序逻辑电路除有组合电路外,还有存储电路。具有记忆能力。第10章时序逻辑电路电工和电子技术(下)10.1双稳态触发器触发器的两个重要特点:(1)触发器有两个可能的稳定工作状态——0和1(2)触发器具有记忆功能10.1.110.1.1基本基本RSRS触发器触发器&&RDSDQQ••SDRDQQ逻辑符号第10章时序逻辑电路电工和电子技术(下)&&RDSDQQ••101010Qn=1,Qn=0则Qn+1=0,Qn+1=1实际上,根据与非门有0出1的原则,无论触发器初态怎样,输出都为0(1)设SD=1,RD=0第10章时序逻辑电路电工和电子技术(下)&&RDSDQQ••011010&&RDSDQQ••111010则Qn=Qn+1Qn=0,Qn=1则Qn+1=1,Qn+1=0即保持状态不变(2)设SD=0,RD=1(3)设SD=RD=1第10章时序逻辑电路电工和电子技术(下)&&RDSDQQ••0011禁用SDRDQnQn+1特性表(4)SD=RD=0110011111010100001010111000禁用001禁用第10章时序逻辑电路电工和电子技术(下)简化特性表QnRDSD0001111001000111ΦΦ卡诺图利用约束项化简,可得基本RS触发器的特征方程为:_1nnDDQSRQ__1DDRS00不定,禁止SDRDQ10001111不变第10章时序逻辑电路电工和电子技术(下)禁用禁用不定波形图DRDSQQ第10章时序逻辑电路电工和电子技术(下)例基本RS触发器的应用&&RDSDQQ••ABS+5V+5VA--〉BB--〉AVAVBQ第10章时序逻辑电路电工和电子技术(下)SDRDQnQn+1特性表000000111010100001010111110禁用111禁用≥1RDSDQQ••≥1或非门组成的基本RS触发器QQRDSDRS第10章时序逻辑电路电工和电子技术(下)10.1.1同步RS触发器时钟脉冲电路符号RDSDCPQQSR&&ABQQRD&&RSDCDSCP第10章时序逻...