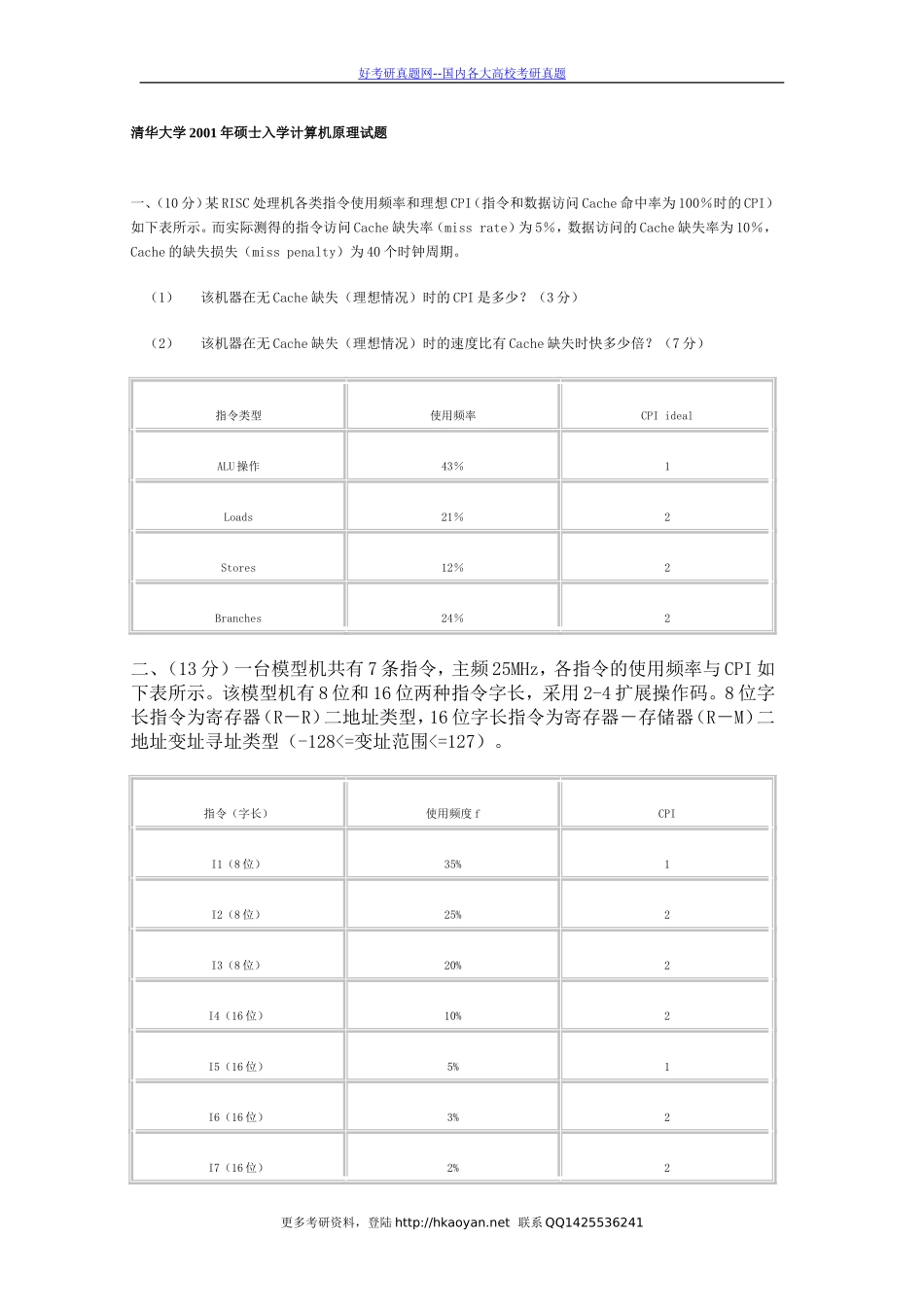

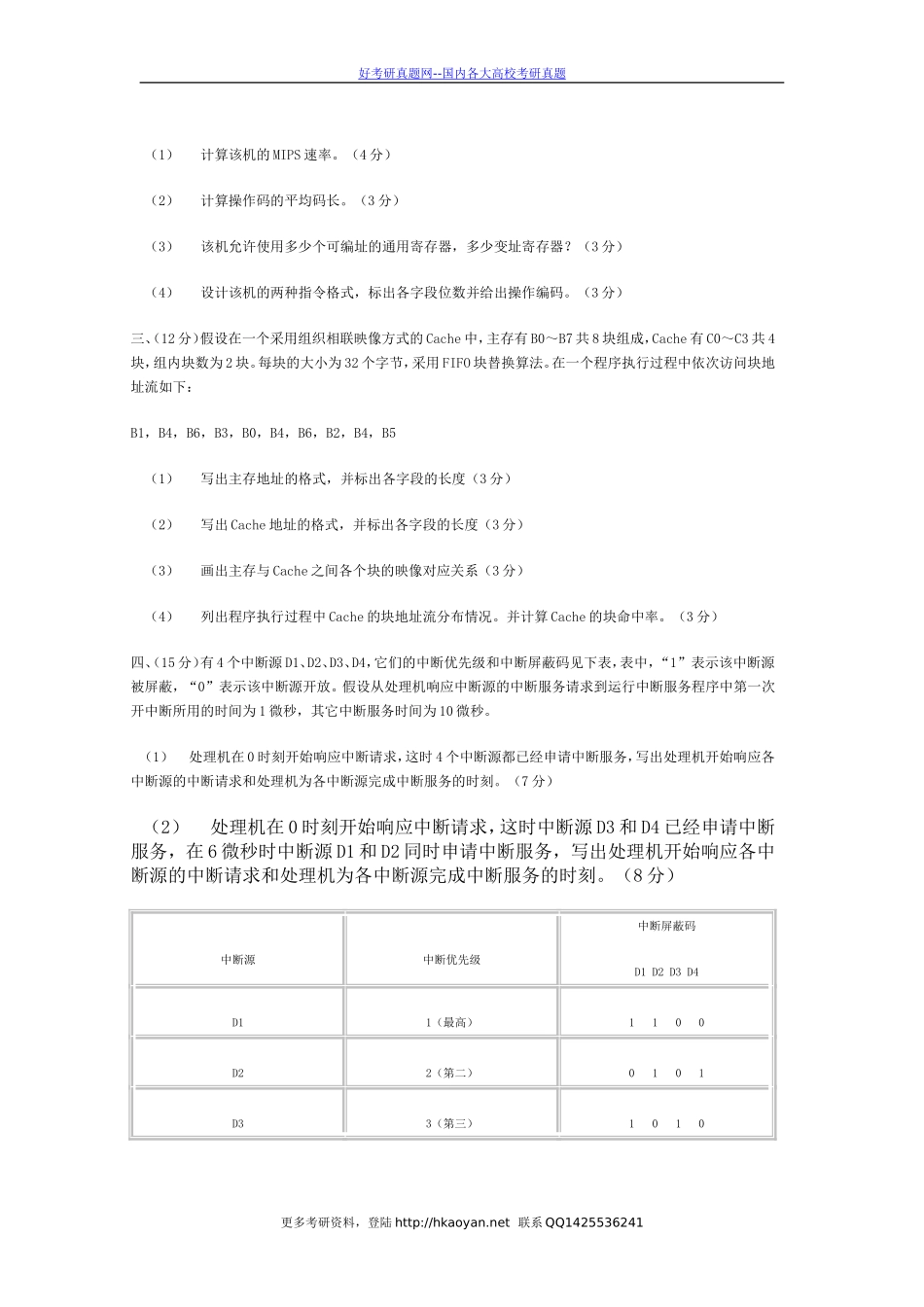

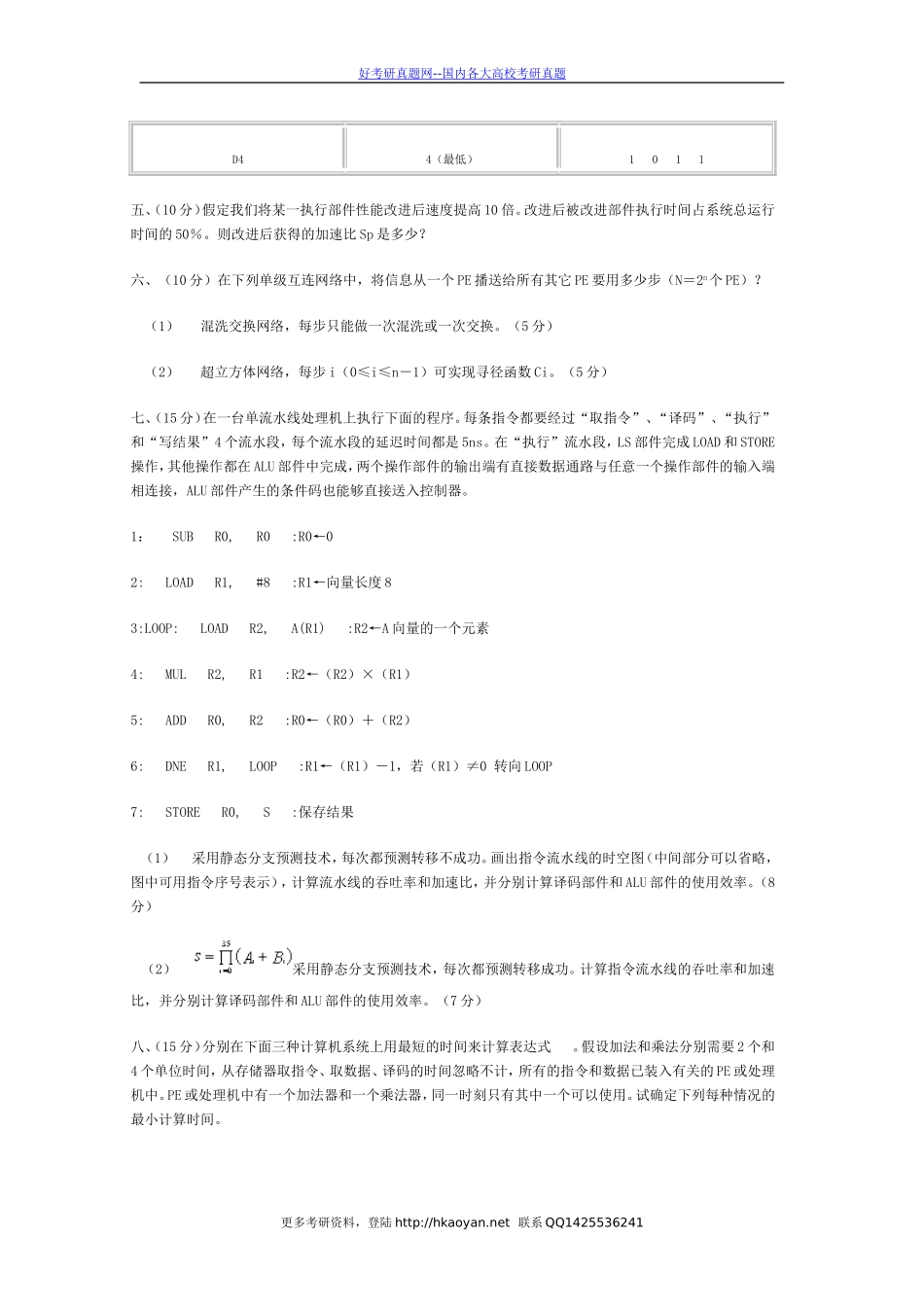

好考研真题网--国内各大高校考研真题清华大学2001年硕士入学计算机原理试题一、(10分)某RISC处理机各类指令使用频率和理想CPI(指令和数据访问Cache命中率为100%时的CPI)如下表所示。而实际测得的指令访问Cache缺失率(missrate)为5%,数据访问的Cache缺失率为10%,Cache的缺失损失(misspenalty)为40个时钟周期。(1)该机器在无Cache缺失(理想情况)时的CPI是多少?(3分)(2)该机器在无Cache缺失(理想情况)时的速度比有Cache缺失时快多少倍?(7分)指令类型使用频率CPIidealALU操作43%1Loads21%2Stores12%2Branches24%2二、(13分)一台模型机共有7条指令,主频25MHz,各指令的使用频率与CPI如下表所示。该模型机有8位和16位两种指令字长,采用2-4扩展操作码。8位字长指令为寄存器(R-R)二地址类型,16位字长指令为寄存器-存储器(R-M)二地址变址寻址类型(-128<=变址范围<=127)。指令(字长)使用频度fCPII1(8位)35%1I2(8位)25%2I3(8位)20%2I4(16位)10%2I5(16位)5%1I6(16位)3%2I7(16位)2%2更多考研资料,登陆http://hkaoyan.net联系QQ1425536241好考研真题网--国内各大高校考研真题(1)计算该机的MIPS速率。(4分)(2)计算操作码的平均码长。(3分)(3)该机允许使用多少个可编址的通用寄存器,多少变址寄存器?(3分)(4)设计该机的两种指令格式,标出各字段位数并给出操作编码。(3分)三、(12分)假设在一个采用组织相联映像方式的Cache中,主存有B0~B7共8块组成,Cache有C0~C3共4块,组内块数为2块。每块的大小为32个字节,采用FIFO块替换算法。在一个程序执行过程中依次访问块地址流如下:B1,B4,B6,B3,B0,B4,B6,B2,B4,B5(1)写出主存地址的格式,并标出各字段的长度(3分)(2)写出Cache地址的格式,并标出各字段的长度(3分)(3)画出主存与Cache之间各个块的映像对应关系(3分)(4)列出程序执行过程中Cache的块地址流分布情况。并计算Cache的块命中率。(3分)四、(15分)有4个中断源D1、D2、D3、D4,它们的中断优先级和中断屏蔽码见下表,表中,“1”表示该中断源被屏蔽,“0”表示该中断源开放。假设从处理机响应中断源的中断服务请求到运行中断服务程序中第一次开中断所用的时间为1微秒,其它中断服务时间为10微秒。(1)处理机在0时刻开始响应中断请求,这时4个中断源都已经申请中断服务,写出处理机开始响应各中断源的中断请求和处理机为各中断源完成中断服务的时...