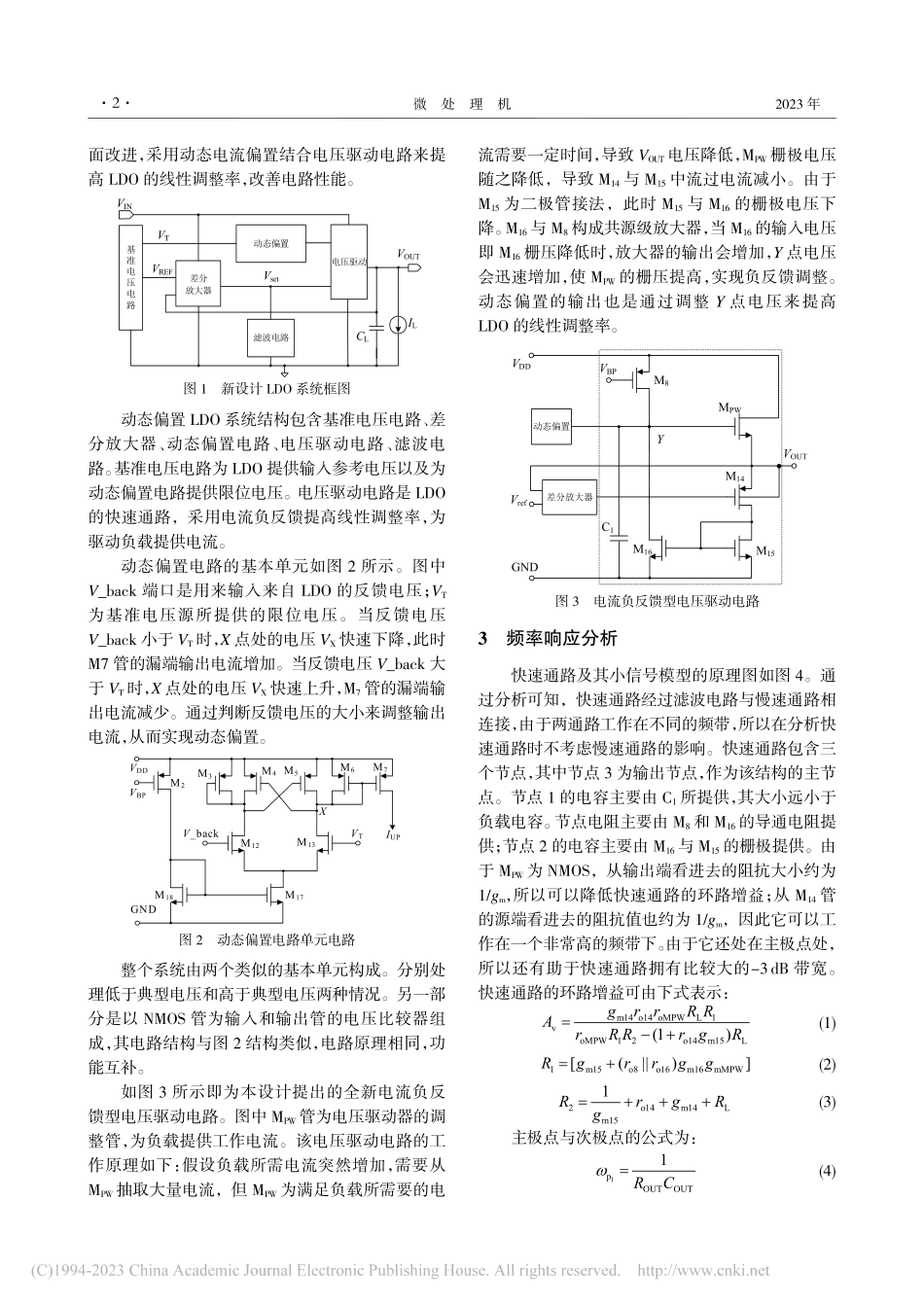

·大规模集成电路设计、制造与应用·1引言随着5G通信和可穿戴设备等市场的快速增长,IC设计向高集成、低功耗转型。为顺应发展潮流,LDO也趋于低功耗和高性能的设计。例如文献[1]中提出基于FVF的无片外电容LDO,在1.2V电源下静态消耗电流13.2μA,下冲电压为341mV。文献[2]提出全集成超快速瞬态LDO,静态电流100μA,恢复时间150ns。文献[3]提出了高PSR的采用FFRC技术的LDO,静态电流为50μA。韩旭等人[4]通过偏置电流辅助电路改善LDO转换速率,其输出电压为1.2V,当负载电流从1mA跳变到100mA时,过冲电压为285mV,静态工作电流为19μA。周梦嵘等[5]采用密勒补偿保证系统稳定实现低功耗,LDO整体消耗电流为17.7μA。张吉伟等[6]提出的低功耗LDO电路采用了零点补偿,低功耗下模式下,静态电流为3.75μA。梁绪亮等人[7]提出LDO片内补偿设计,电压过冲很低但静态工作电流为5μA。基于现有成果,以进一步降低功耗和减小过冲电压为目标,本研究尝试提出一种全新的设计方案。2电路结构设计新设计的LDO系统框图如图1所示。与传统低压差线性稳压器相比,在电压驱动电路方面做出全一种低功耗无片外电容低压差线性稳压器设计*任建,袁申,辛晓宁,姜龙(沈阳工业大学信息科学与工程学院,沈阳110870)摘要:为降低LDO稳压器在芯片中的占用面积、减小待机状态下的电流消耗,设计一种低功耗、无片外电容的新型LDO。设计中采用动态电流偏置电路以及全新的电流负反馈型电压驱动电路,来提高LDO线性调整率。通过实验与其他设计方案对比,观察在一定输入电压、输出电压条件下,负载电流变化对最大上冲电压、下冲电压的影响。新设计LDO在空载条件下消耗的电流为3.13μA,在降低功耗同时提高了过充电压抑制能力,有着明显的产品优势,低功耗应用前景广阔。关键词:低压差线性稳压器;无片外电容;线性调整率;动态置偏;低功耗DOI:10.3969/j.issn.1002-2279.2023.02.001中图分类号:TN402文献标识码:A文章编号:1002-2279(2023)02-0001-04DesignofaLow-PowerLDOLinearRegulatorwithoutOff-ChipCapacitorRENJian,YUANShen,XINXiaoning,JIANGLong(SchoolofInformationScienceandEngineering,ShenyangUniversityofTechnology,Shenyang110870,China)Abstract:InordertoreducetheoccupiedareaofLDOregulatorinthechipandreducethecurrentconsumptioninstandbystate,anewLDOregulatorwithlowpowerconsumptionandnooff-chipcapacitanceisdesigned.Inthedesign,dynamiccurrent...