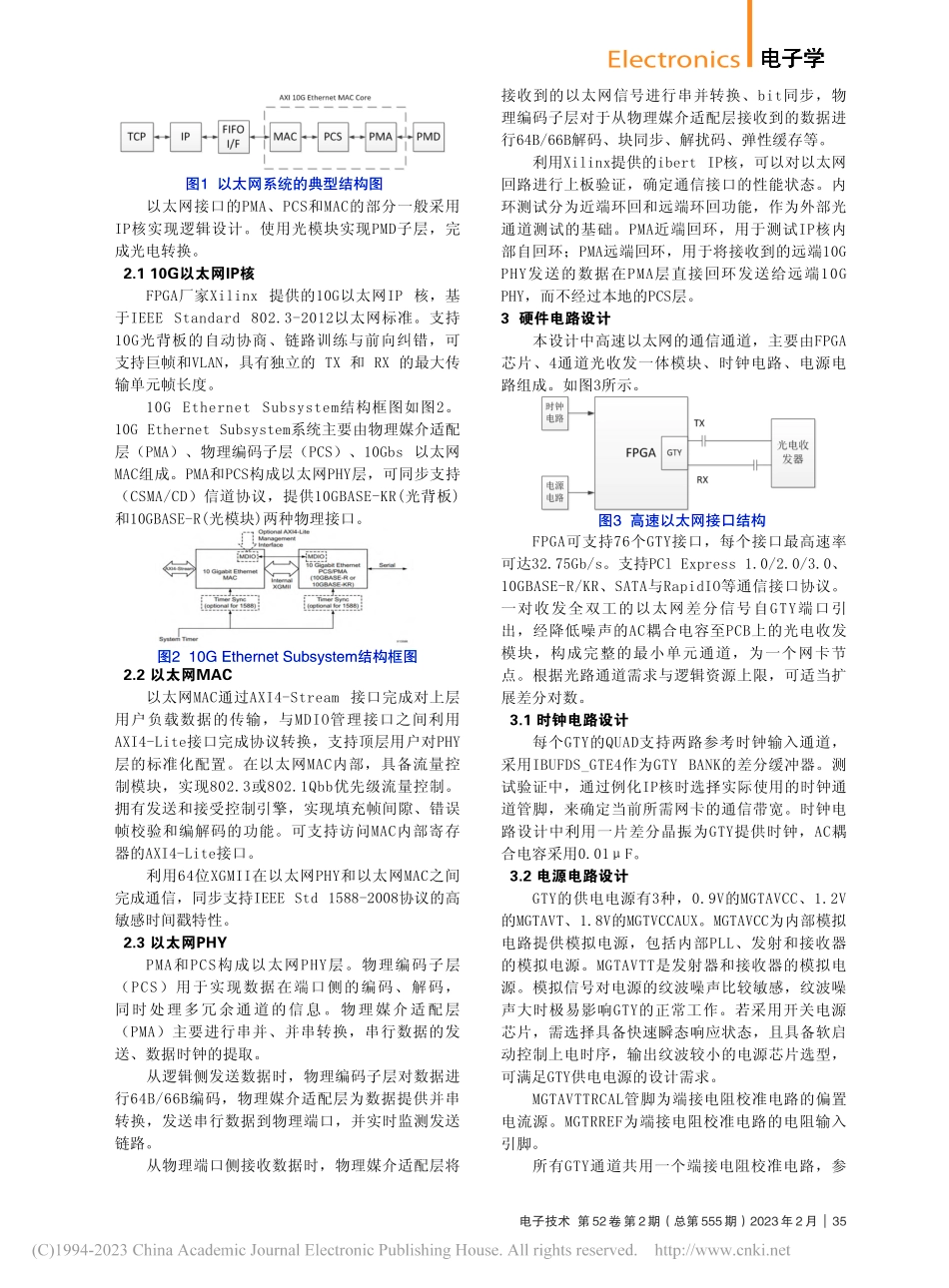

34电子技术第52卷第2期(总第555期)2023年2月Electronics电子学32.75Gb/s速率的GTY接口。UltrascaleFPGA较上一代28nmvirtex系列,系统功耗比可提升2~5倍,较V7FPGA逻辑工作频率提升一倍。FPGA高系统集成度与智能化的迭代,推动高速接口的硬件设计也同步进行优化调整。相较上一代7系列产品,Ultrascale系列FPGA在以下方面有进一步优化。(1)可配置逻辑块CLB。UltraScale架构具备更高性能和低功耗的可编程逻辑资源,提供了高敏捷度的超前进位逻辑。UltraScaleFPGA将原本7系FPGA内2个独立SLICE组合至一个,其具备的不同长度的垂直、水平布线资源,可以跨越多个CLB。通过这种灵活动态布线的方式,UltraScaleFPGA可提供源节点到目的节点的高效传输,改善了运算结果和逻辑运行时间。(2)块存储器资源BRAM。UltraScaleFPGA支持不同独立BRAM(块存储器资源)之间存储数据的共享,保留每个BRAM的独立端口。根据逻辑资源使用程度的不同需求,可通过CLK和RST控制垂直相邻的BRAM的读写,可灵活拓展FIFO和内存阵列的深度、大小,节约FPGA运行功耗。2高速以太网通信结构以太网系统的典型结构图如图1所示。0引言随着通信技术的高速发展,航空电子网络设备对于网络带宽要求日益增加。传统网卡架构中,CPU依靠嵌入式操作系统处理DMA中断请求,发起相应网络协议栈,处理通信数据缓冲信息。DPDK利用轮询方式访问通信缓冲数据,虽然规避了主机中断,降低软件开销,但对于网络I/0带宽的改善没有起到本质性帮助。近年出现的智能网卡硬件架构,将原本接口总线与存储带宽匹配的侧重点,转移至网络I/0带宽匹配,该结构依赖于网卡硬件可提供良好、稳定的超万兆级高速以太网通信[1]。针对当前网卡不断迭代的数据大带宽与数据大容量需求,高速以太网的电路设计无法沿用传统百兆级的设计方法,对超高速以太网的硬件设计进行验证与仿真具有重要意义[2]。本文以UltraScale系列FPGA为例,分析了高速以太网的IP核架构,针对网卡高速以太网电路的具体设计要求,对UltraScale的高速接口电路进行原理设计与EDA实现,最后进行高速信号完整性仿真与验证。1UltrascaleFPGAUltrascale系列FPGA采用20nm的制作工艺,可支持数百Gb级的速率带宽。内部集成BRAM75.9Mb,逻辑单元2586K,集成9个100G以太网MAC,支持76个作者简介:崔钟允,中国航空工业集团公司西安航空计算技术研究所,硕士;研究方向:机载通信技术。收稿日期:2023-01-16;修回日期:2023-02-12。摘要:阐述UltraScaleFPGA高...